*Областное государственное бюджетное

образовательное учреждение

среднего профессионального образования

«Иркутский авиационный техникум»*

УТВЕРЖДАЮ

Директор ОГБОУ СПО «ИАТ»

\_\_\_\_\_ В.Г. Семенов

**Комплект методических указаний по выполнению

практических работ по междисциплинарному курсу

МДК.01.02 Проектирование цифровых устройств**

образовательной программы (ОП)

по специальности СПО

230113 Компьютерные системы и комплексы

базовой подготовки

**Иркутск 2013**

## Задание1 Построение простейших схем

В данном задании рассматриваются простейшие элементы цифровых схем и их применение для создания цепей генерации и схем задержки.

### Генераторы синхросигналов

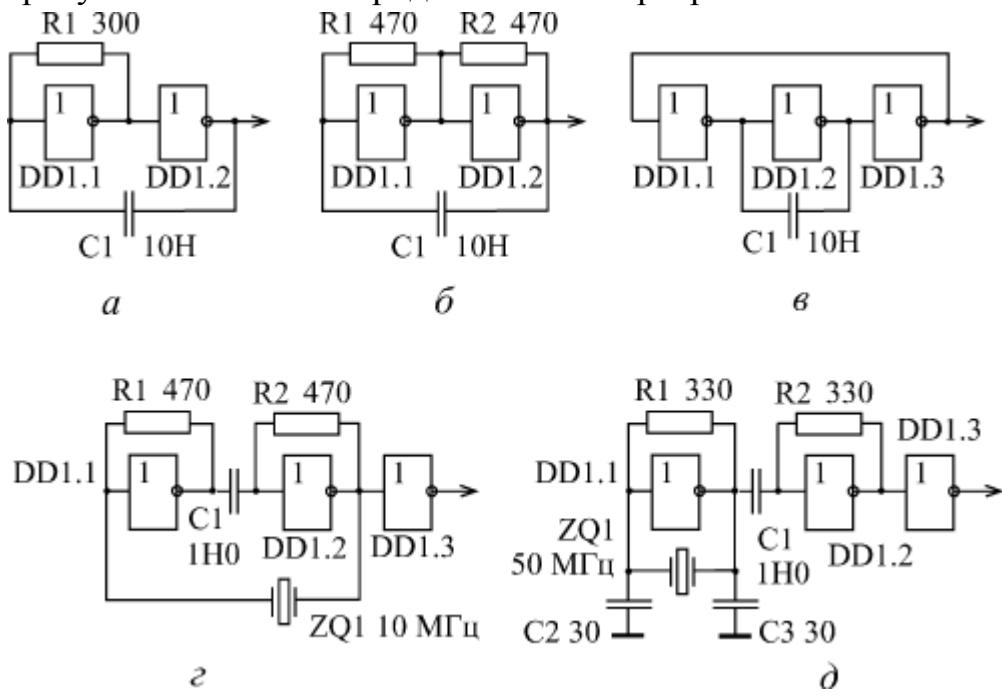

Часто инверторы применяются в схемах генераторов прямоугольных импульсов (рисунок 3), выходной сигнал которых периодически меняется с нулевого уровня на единичный и обратно. Все приведенные на рисунке схемы, кроме схемы (д), выполнены на элементах К155ЛН1, но могут быть реализованы и на инверторах других серий при соответствующем изменении номиналов резисторов. Например, для серии К555 номиналы резисторов увеличиваются примерно втрое. Схема (д) выполнена на элементах КР531ЛН1, так как она требует высокого быстродействия инверторов.

Рисунок 3 - Схемы генераторов импульсов на инверторах

Схемы (а, б) и в представляют собой обычные RC-генераторы, характеристики которых (выходную частоту, длительность импульса) можно рассчитать только приблизительно. Для схем (а и б) при указанных номиналах резистора и конденсатора частота генерации составит порядка 100 кГц, для схемы (в) — около 1 МГц. Эти схемы рекомендуется использовать только в тех случаях, когда частота не слишком важна, а важен сам факт генерации. Если же точное значение частоты принципиально, то рекомендуется применять схемы

(г и д), в которых частота выходного сигнала определяется только характеристиками кварцевого резонатора.

### Описание работы генератора импульсов (рисунок 3а)

Схема имеет два динамических состояния. В первом из них, когда на выходе D1.1 состояние логический уровень - "1" (выход D1.2 логический уровень - "0"), конденсатор C1 заряжается. В процессе заряда напряжение на входе инвертора D1.1 возрастает, и при достижении значения  $U_{\text{пор}}=0,5U_{\text{пит}}$  происходит скачкообразный переход во второе динамическое состояние, в котором на выходах D1.1 логический уровень - "0", D1.2 - "1". В этом состоянии происходит перезаряд емкости (разряд) током обратного направления. При достижении напряжения на C1  $U_{\text{пор}}$  происходит возврат схемы в первое динамическое состояние. При использовании неполярного конденсатора C1 длительность импульсов ( $t_i$ ) и пауза ( $t_o$ ) будут почти одинаковыми:  $t_i=t_o=0,7R_1C_1$ . Полный период  $T=1,4R_1C_1$ . Резистор R1 и конденсатор C1 могут находиться в диапазоне 20 кОм...10 МОм; 300 пФ...100 мКФ.

Схема (г) используется для кварцевого резонатора, работающего на первой (основной) гармонике. Величину емкости можно оценить по формуле:

$$C > 1/(2RF)$$

где F — частота генерации. Схема д применяется для гармониковых кварцевых резонаторов, которые работают на частоте, большей основной в 3, 5, 7 раз (это бывает нужно для частот генерации выше 20 МГц).

### Схемы задержки

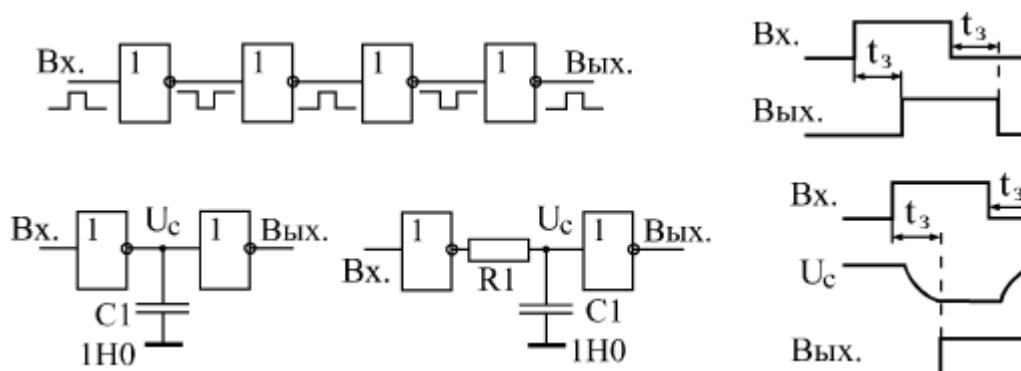

Инверторы также применяются в тех случаях, когда необходимо получить задержку сигнала, правда, незначительную (от 5 до 100 нс). Для получения такой задержки последовательно включается нужное количество инверторов (рисунок 4). Суммарное время задержки, например, для четырех инверторов, можно оценить по формуле:  $t_3 = 2t_{\text{PHL}} + 2t_{\text{PLH}}$

#### Рисунок 4 - Использование инверторов для задержки сигнала

Необходимо учитывать, что обычно реальные задержки элементов оказываются существенно ниже (иногда даже вдвое), чем табличные параметры  $t_{PHL}$  и  $t_{PLH}$ . То есть о точном значении получаемой задержки говорить не приходится, ее можно оценить только примерно.

Для задержки сигнала используются также конденсаторы. При этом задержка возникает из-за медленного заряда и разряда конденсатора (напряжение на конденсаторе —  $U_C$ ). Схема без резистора (слева на рисунке) дает задержку около 100 нс. В схеме с резистором (справа на рисунке) номинал резистора должен быть порядка сотен Ом. Но при выборе таких схем с конденсаторами надо учитывать, что некоторые серии микросхем (например, КР1533) плохо работают с затянутыми фронтами входных сигналов. Кроме того, надо учитывать, что количество времязадающих конденсаторов в схеме обратно пропорционально уровню мастерства разработчика схемы.

#### Задание 2 Расчет генератора и схемы задержки сигнала

Рассчитать сопротивление  $R_1$  и емкость  $C_1$  для генератора, приведенного на рисунке 3а, для частоты 32КГц и частоты 100КГц, заполнить таблицу 2.

Таблица 2 – Расчетные параметры генератора

| $R_1$ , КОм | $C_1$ , мкФ | $T$ , нс | $F$ , КГц |

|-------------|-------------|----------|-----------|

|             |             |          | 32        |

|             |             |          | 100       |

Рассчитать задержку прохождения цифрового сигнала для  $t_3 = 300$  нс, 100нс. Заполнить таблицу 3.

Таблица 3 – Расчетные параметры цепи задержки

| $t_3$ , нс | $2t_{PHL}$ , нс | $2t_{PLH}$ , нс | Количество лог. элементов |

|------------|-----------------|-----------------|---------------------------|

| 300        |                 |                 |                           |

| 100        |                 |                 |                           |

Самостоятельно ответить на следующие вопросы:

1. Как обеспечить стабилизацию частоты в генераторе?

2. Чем обусловлена различное время задержки для различных элементов

3. Увеличится ли частота при увеличении ёмкости конденсатора RC – генератора.

частоты от ем-

Объяснить зависимость кости.

**со справочником**

В данном задании закрепите со справочной литерату-

ряются навыки по работе.

K155TM2 (2 D-

триггера)

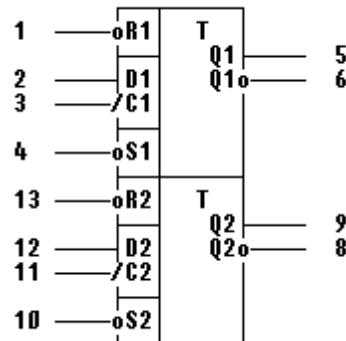

Микросхема представляет собой два независимых D-триггера, срабатывающих по положительному фронту тактового сигнала. На рисунке 5 представлено УГО триггера K155TM2.

Рисунок 5 –УГО K155TM2

Корпус K155TM2 типа 201.14-2 (DIP 14). В одном корпусе находится 2 элемента. На рисунке 6 приведена таблица истинности для рассматриваемого элемента.

В таблице 4 приведены электрические параметры

*Таблица истинности*

| ВЫХОДЫ |   |      |   | ВХОДЫ |  |

|--------|---|------|---|-------|--|

| S      | R | C    | D | Q     |  |

| L      | H | x    | x | H     |  |

| H      | L | x    | x | L     |  |

| L      | L | x    | x | ?     |  |

| H      | H | LtoH | H | H     |  |

| H      | H | LtoH | L | L     |  |

| H      | H | L    | x | Qo    |  |

?-неопределённое состояние выхода

Рисунок 6

Таблица 4 - Электрические параметры

|    |                                                                          |                                      |

|----|--------------------------------------------------------------------------|--------------------------------------|

| 1  | Номинальное напряжение питания                                           | 5 В ±5 %                             |

| 2  | Выходное напряжение низкого уровня                                       | не более 0,4 В                       |

| 3  | Выходное напряжение высокого уровня                                      | не менее 2,4 В                       |

| 4  | Напряжение на антезвонном диоде                                          | не менее -1,5 В                      |

| 5  | Входной ток низкого уровня<br>по входам 2,4,10,12<br>по входам 1,3,11,13 | не более -1,6 мА<br>не более -3,2 мА |

| 6  | Входной ток высокого уровня<br>по входам 2,12<br>по входам 4,3,11,10     | не более 0,04 мА<br>не более 0,08 мА |

| 7  | Входной пробивной ток                                                    | не более 1 мА                        |

| 8  | Ток короткого замыкания                                                  | -18...-55 мА                         |

| 9  | Ток потребления                                                          | не более 30 мА                       |

| 10 | Потребляемая статическая мощность на один триггер                        | не более 78,75 мВт                   |

| 11 | Время задержки распространения при включении                             | не более 40 нс                       |

| 12 | Время задержки распространения при выключении                            | не более 25 нс                       |

| 13 | Тактовая частота                                                         | не более 15 мГц                      |

Зарубежные аналоги: **SN7474N, SN7474J**

**Задание 5** В рабочей тетради по форме примерного отчета составить описание компонентов, применяемых при проектировании цифровых устройств во время учебной практики.

К155ЛН1, К155ЛА1, К155ЛА2, К155ЛА3, К155ЛИ3, К155ЛЕ1, К155ТМ2, К155ТВ9, К155ИР13, К555ИР23, К155ИД3, К155ИЕ7, К555АП5, К155ИМ3, К155РУ2.

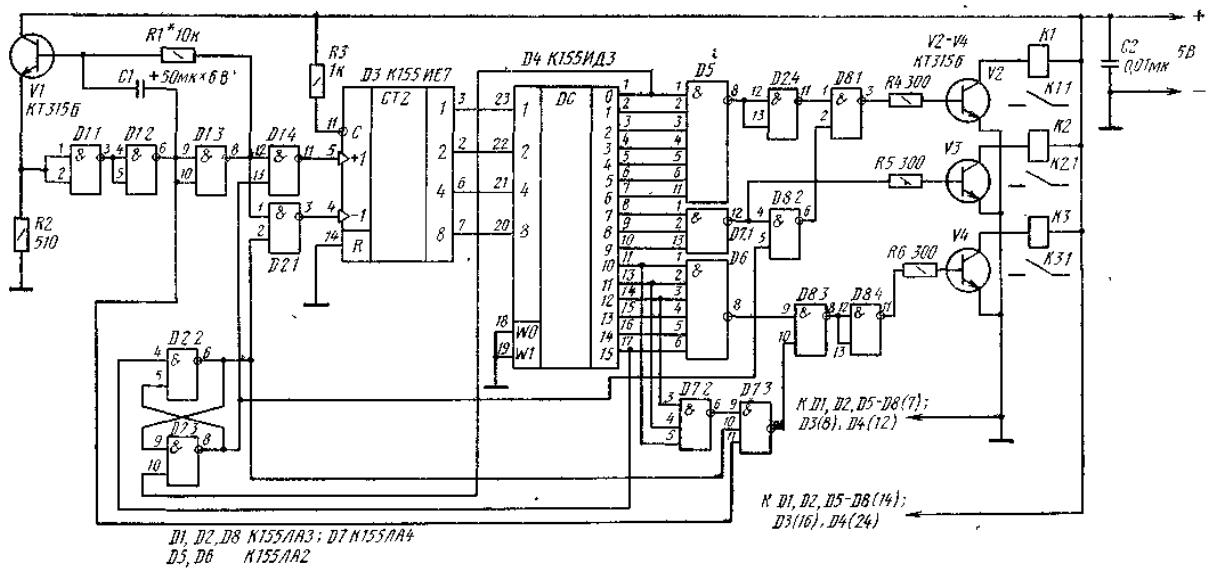

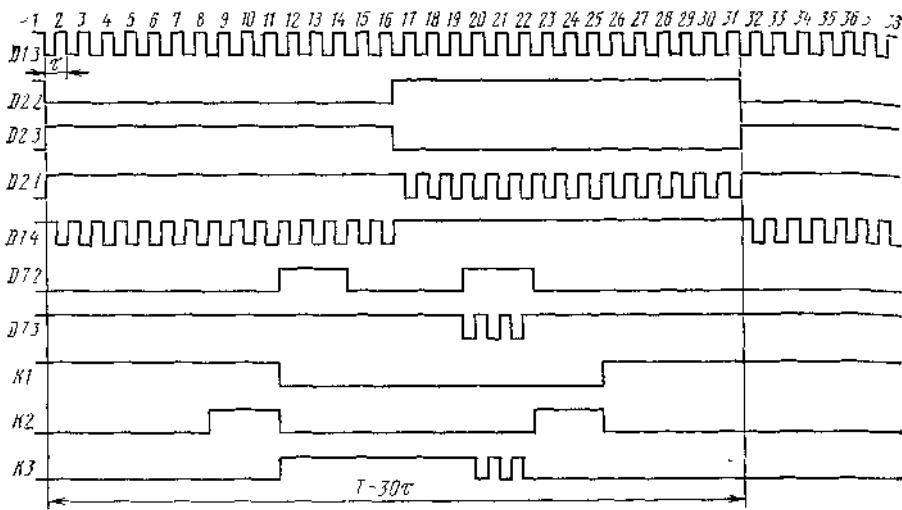

Светофор, схема которого приведена на рис. 32, можно установить на игровом перекрестке детского парка, где ребята катаются на велосипедах, пе- дальных автомобилях. Принцип работы такого электронного автомата иллюстрируют временные диаграммы, изображенные на рис. 33.

Логические элементы D1.1 — D1.3 образуют генератор,рабатывающий импульсы с периодом следования около 1 с. Транзистор VI повышает входное сопротивление элемента D 1.1, что позволило использовать в генераторе конденсатор C1 сравнительно небольшой емкости при большом сопротивлении резистора R1. Импульсы с выхода генератора поступают на входы элементов D1.4 и D2.1, работой которых управляет RS-триггер на элементах D2.2 и D2.3. Если на выводе 6 элемента D2.2 напряжение высокого уровня, то импульсы поступают на вывод 4 микросхемы D3, если же напряжение высокого уровня на выводе 8 элемента D2.3, то импульсы подаются на вывод 5 микросхемы D3. Эта микросхема (К155ИЕ7) — параллельный реверсивный четырехразрядный двоичный счетчик, работающий в коде 1 — 2 — 4 — 8. Ее вход R служит для установки счетчика в нулевое состояние, вход C — для предварительной записи в счетчик информации, поданной на входы (на схеме не показаны). В данном случае на вход C постоянно подается напряжение высокого уровня, а на вход R — низкого уровня. При подаче счетных импульсов на вход +1 происходит увеличение числа, записанного в счетчике (прямой счет); если же импульсы подавать на вход — 1, то число будет уменьшаться.

Сигналы с четырех выходов счетчика поступают на входы дешифратора Т4 (К155ИД3). В любой момент времени на одном из выходов этого дешифратора появляется напряжение низкого уровня, причем номер этого выхода соответствует двоичному эквиваленту числа, поданного на вход дешифратора.

Рассмотрим работу устройства при прямом счете импульсов. Когда на выходе элемента D2.3 напряжение высокого уровня, на выходе элемента D2.2 — напряжение низкого уровня (см.. рис. 33). Импульсы с генератора через элемент D1.4 поступают на вход +1 микросхемы D3. При этом происходит увеличение числа, записанного в счетчике, и напряжение низкого уровня появляется последовательно на выходах микросхемы D4. Пока напряжение низкого уровня присутствует на выводах 1, 2,..., 7 микросхемы D4, на выходе микросхемы D5 — напряжение высокого уровня. В это время на выходе элемента D8.1 будет напряжение высокого уровня, сработает реле K1 и своими

контактами K1.1 замкнет цепь питания лампы красного цвета (на схеме не показана). Лампы желтого и зеленого сигналов в это время не горят, так как на выходах элементов D7.1 и D8.4 — напряжение низкого уровня. При появлении напряжения низкого уровня на выводах 8, 9, 10 микросхемы D4 на выходе элемента D7.1 появится напряжение высокого уровня, сработает реле K2 и загорится лампа желтого сигнала. Но продолжает гореть и, красная лампа, так как на выходе элемента D8.2 напряжение низкого уровня, а на выходе элемента D8.1 — по-прежнему напряжение высокого уровня (заметим: при обратном счете импульсов при напряжении низкого уровня на выводах 8, 9, 10 микросхемы D4 на выходе элемента D8.2 будет напряжение высокого уровня, так как RS-триггер D2.2, D2.3 находится уже в другом состоянии). При дальнейшем счете импульсов напряжение низкого уровня появляется последовательно на выводах 11, 12,..., 16 микросхемы D4. В это время реле K1 и K2 отпустят, а реле K3 срабатывает, потому что на выходе микросхемы D6 появляется напряжение высокого уровня, и на выходах элементов D7.3 и D8.4 — также напряжение высокого уровня.

Рисунок 1 Схема электронного светофора

Рисунок 2 Временные диаграммы работы электронного светофора

Горит лампа зеленого сигнала светофора. Когда напряжение низкого уровня появится на выводе 17 микросхемы D4, триггер на элементах D2.2, D2.3 переключится в противоположное состояние (см. импульс № 16 на рис. 33). Теперь импульсы будут поступать на вход — 1 микросхемы D3, и счет будет происходить в обратном направлении. Лампа зеленого сигнала светофора продолжает гореть. Когда же напряжение низкого уровня появляется последовательно на выводах 14, 13 и 11 микросхемы D4, зеленый сигнал «мигает». Это обеспечивается подачей напряжения высокого уровня на выводы 9 и 10 элемента D7.3 и импульсов с генератора на вывод 11 этого же элемента. При появлении напряжения низкого уровня на выводах 10, 9, 8 микросхемы D4 сработает реле K2, а реле K3 отпускает. При дальнейшем счете импульсов загорится лампа красного сигнала. При появлении напряжения низкого уровня на выводе 1 микросхемы D4 триггер D2.2, D2.3 переключается, начинается прямой счет импульсов, и весь цикл работы автомата повторяется.

Частоту генератора, а следовательно, и время горения сигнальных ламп светофора можно изменять подбором резистора R1.

Вместо микросхем серии К155 можно использовать аналогичные микросхемы серии К133. Все резисторы — МЛТ-0,25; конденсатор C1 — К50-6,

К53-1 или К50-3; С2 — КЛС, КМ-6, К10-7В. Транзисторы КТ315Б (VI — V4) можно заменить на МП38, КТ312, КТ601 с любыми буквенными индексами. Реле К1 — К3 — типа РЭС-10 (паспорт РС4.524.304). Нормально разомкнутые контакты этих реле включают последовательно в цепи питания ламп светофора: К1 — с красной, К2.1 — с желтой и К3.1 — с зеленой лампами.

Не следует забывать, что контакты реле РЭС-10 могут коммутировать постоянное напряжение 30 В при токе 2 А или же постоянное напряжение 250 В при токе 0,3 А. Поэтому желательно применять 36-вольтовые осветительные лампы мощностью 40 Вт, питая их от понижающего трансформатора через двухполупериодный выпрямитель, или же использовать лампы на напряжение 220 В и мощностью до 60 Вт, также питая их постоянным током. Можно также применять промежуточные реле, рассчитанные на коммутацию переменного тока (например, МКУ-48).

Для уменьшения обгорания контактов реле параллельно им следует включить искрогасящие цепи, каждая из которых состоит из последовательно соединенных резистора сопротивлением 100... 200 Ом и конденсатора емкостью 0,1 ... 0,5 мкФ. Мощность рассеяния резистора должна быть не менее 0,5 Вт, номинальное напряжение конденсатора — не менее 300 В,

Монтаж устройства выполняют на унифицированной печатной плате: выводы элементов припаивают к контактным площадкам платы, а соединения между ними делают отрезками одножильного изолированного провода.

Правильно собранное устройство начинает работать сразу после включения и дополнительного налаживания не требует.

Подумайте: как можно превратить этот светофор в «мигалку»? Такие светофоры устанавливают на перекрестках улиц с небольшим движением транспорта.

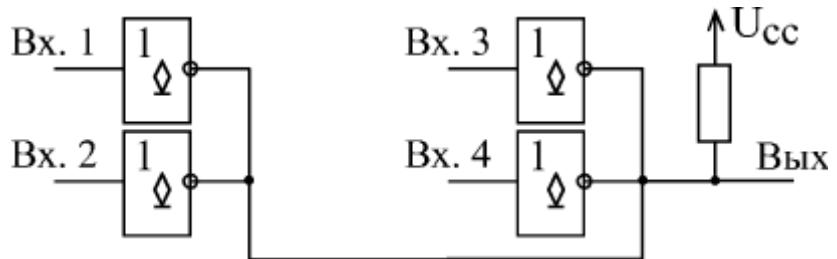

## **Монтажное ИЛИ**

Еще одно применение *инверторов*, но только с выходом ОК, состоит в построении на их основе так называемых элементов "*Проводного ИЛИ*". Для этого выходы нескольких *инверторов* с выходами ОК объединяются, и через

резистор присоединяются к источнику питания ([рисунок 3](#)). Выходом схемы является объединенный выход всех элементов. Такая конструкция выполняет логическую функцию ИЛИ-НЕ, то есть на выходе будет сигнал логической единицы только при нулях на всех входах. Но о логических функциях подробнее будет рассказано далее.

Рисунок 3 Объединение выходов инверторов с ОК для функции ИЛИ-НЕ

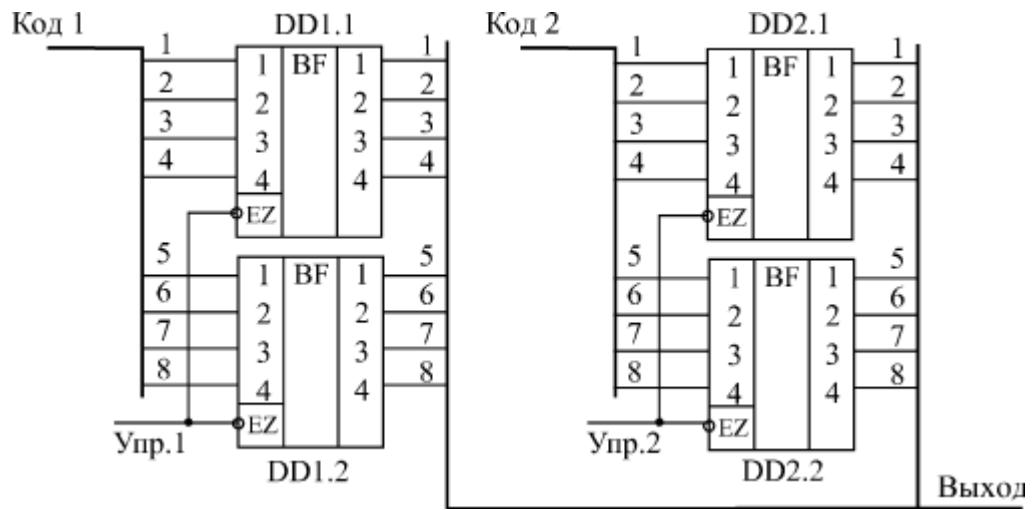

### Буферные схемы (шинные формирователи)

Очень часто надо обрабатывать не одиночные сигналы, а группы сигналов, например, сигналы, передающие многоразрядные коды (примером служат шины данных ПЭВМ, микроконтроллеров, интерфейсы). В этом случае удобно применять буферы с групповым управлением. То есть имеющие один вход разрешения EZ для нескольких выходов. Примерами могут служить микросхемы АП5 (восемь буферов, разделенные на две группы по четыре буфера, каждая из которых имеет свой вход управления).

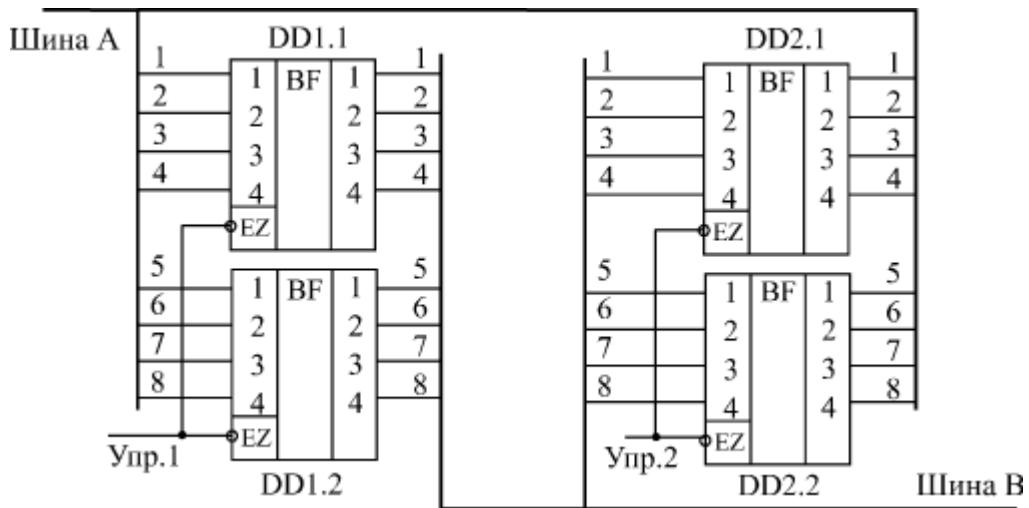

На рисунке 4 показан пример *мультиплексирования* двух восьмиразрядных кодов с помощью двух микросхем АП5. Одноименные выходы обеих микросхем объединены между собой. Пропускание на выход каждого из двух входных кодов разрешается своим управляющим сигналом (Упр. 1 и Упр. 2), причем должен быть исключен одновременный приход этих двух сигналов, чтобы не было конфликтов на выходах.

Рисунок 4 Мультиплексирование двух входных кодов с помощью буферов с 3 состоянием

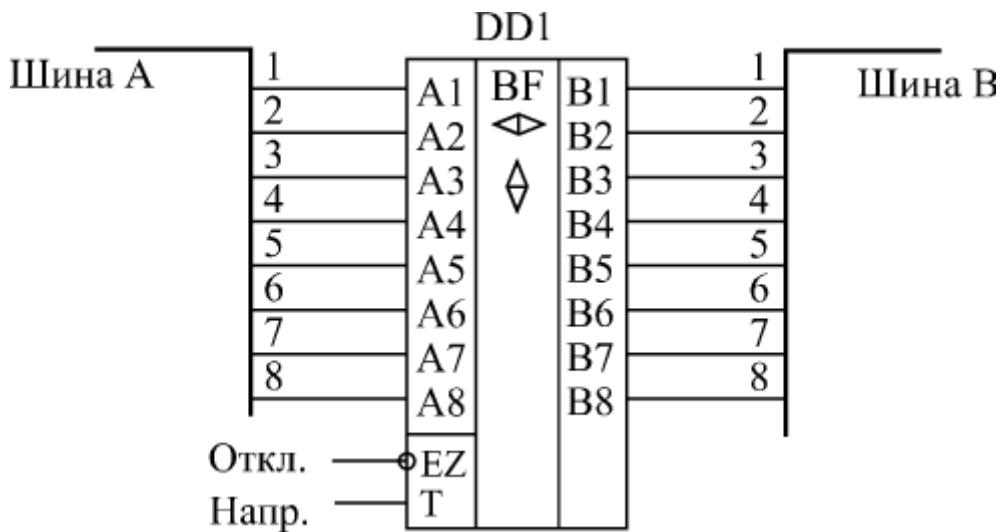

Двунаправленные буфера, в отличие от однона правленных, позволяют передавать сигналы в обоих направлениях. В зависимости от специального управляющего сигнала Т (другое обозначение — BD), входы могут становиться выходами и наоборот: выходы — входами. Обязательно имеется и вход управления третьим состоянием EZ, который может отключить как входы, так и выходы.

На рисунке 5 для примера показан двунаправленный буфер АП6, который может передавать данные между двумя двунаправленными шинами А и В в обоих направлениях. При единичном уровне на управляющем входе Т (сигнал Напр.) данные передаются из шины А в шину В, а при нулевом уровне — из шины В в шину А (таблице 1). Единичный уровень на управляющем входе EZ (сигнал Откл.) отключает микросхему от обеих шин.

Рисунок 5 Включение двунаправленного буфера

**Таблица 1 Таблица истинности двунаправленного буфера**

| Вход Т | Вход-EZ | Операция               |

|--------|---------|------------------------|

| 0      | 0       | B <small>или</small> A |

| 1      | 0       | A <small>или</small> B |

| 0      | 1       | 3С                     |

| 1      | 1       | 3С                     |

Двунаправленную передачу можно организовать и на основе однона правленных буферов. На рисунке 6 показано, как это можно сделать на двух микросхемах АП5. Здесь при нулевом сигнале Упр. 1 информация будет передаваться с шины А на шину В, а при нулевом сигнале на входе Упр. 2 — с шины В на шину А. Если оба входа Упр. 1 и Упр. 2 находятся в единичном состоянии, то шины А и В отключены друг от друга, а подача нулей на оба входа Упр. 1 и Упр. 2 должна быть исключена, иначе состояние обеих шин А и В будет не определено.

Рисунок 6 Организация двунаправленной передачи с помощью односторонних буферов

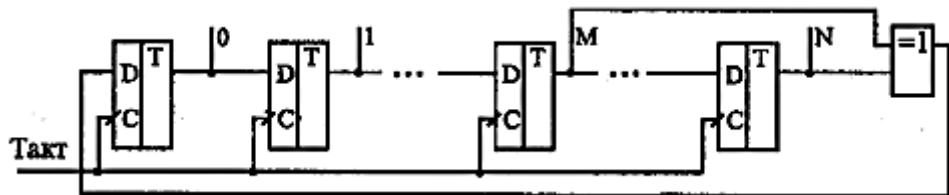

### Генератор псевдослучайной последовательности.

Структура генератора псевдослучайной последовательности.

Выбор номеров разрядов для подключения обратной связи представляет собой непростую задачу, но существуют справочные таблицы, в которых они приведены. В любом случае одна из точек подключения — выход старшего разряда. В табл. 1 приведены точки подключения обратной связи для регистров сдвига с разным количеством разрядов  $N$  (номера разрядов считаются от нуля).

**Таблица 1** Точки подключения обратной связи

| <b>N</b> | <b>7</b> | <b>8</b>   | <b>15</b> | <b>16</b>     | <b>24</b>     | <b>31</b> |

|----------|----------|------------|-----------|---------------|---------------|-----------|

| Выходы   | 6,5      | 7, 6, 4, 2 | 14, 13    | 15, 13, 12,10 | 23, 22, 21,16 | 30,17     |

Из таблицы видно, что выгоднее брать число разрядов не кратное 8, например, 7,15 или 31. В этом случае для обратной связи используются всего

лишь два выхода, то есть достаточно одного двухходового элемента Исключающее ИЛИ. Период выходной последовательности генератора составляет  $(2N - 1)$  тактов, где  $N$  — количество разрядов регистра сдвига. За это время каждое из возможных значений выходного кода (кроме одного) встречается один раз. Количество единиц в выходном сигнале больше количества нулей на единицу.

Выходной код 000...0 представляет собой запрещенное состояние, так как он блокирует работу генератора, воспроизводя сам себя снова и снова. Но в то же время получиться такой нулевой код может только сам из себя, поэтому достаточно обеспечить, чтобы его не было при включении питания схемы. Частоты в спектре выходного сигнала будут следовать с интервалом  $f_T / (2N - 1)$ , а огибающая спектра будет практически постоянной до частоты  $0,25f_T$ , то есть шум до этой частоты можно считать белым (спад в 3 дБ происходит на частоте  $0,45 f_T$ ).

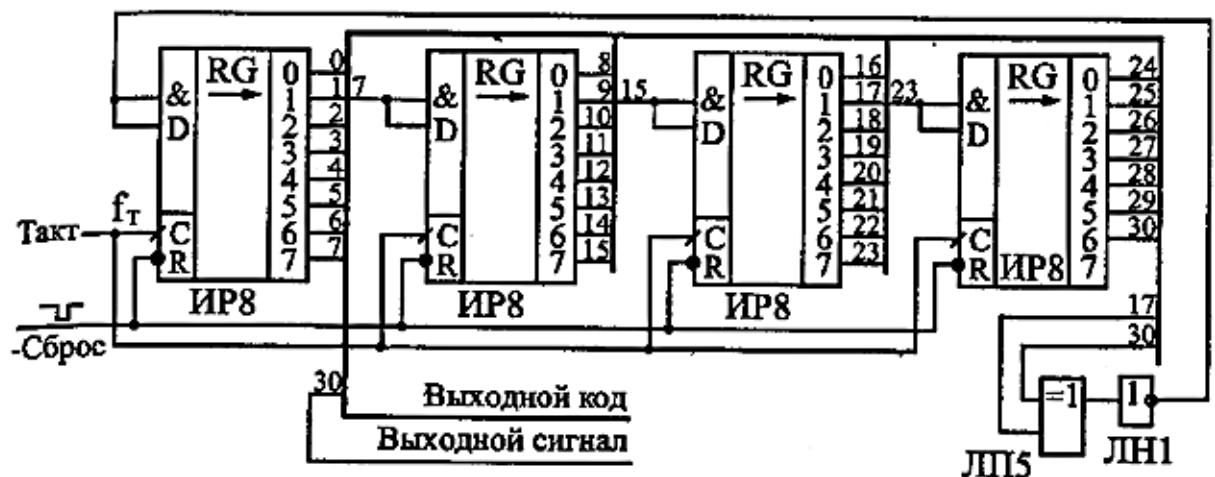

На рисунке.2 показана практическая схема генератора псевдослучайной последовательности на 31-разрядном сдвиговом регистре. Обратная связь осуществляется с выходов 30 и 17 регистра через двухходовой элемент Исключающее ИЛИ с инвертором. Из-за применения инвертора запрещенным состоянием генератора является код 1111...1 (а не код 000...0), который в данном случае исключается очень просто — начальным сбросом регистров в нуль при включении питания по сигналу -Сброс. Генератор выдает квазислу-

чайную последовательность 31-разрядных кодов со всех выходов регистра, а также квазислучайную последовательность нулей и единиц на любом из выходов регистра. Такой генератор использовала известная фирма Hewlett-Packard в своем генераторе шума.

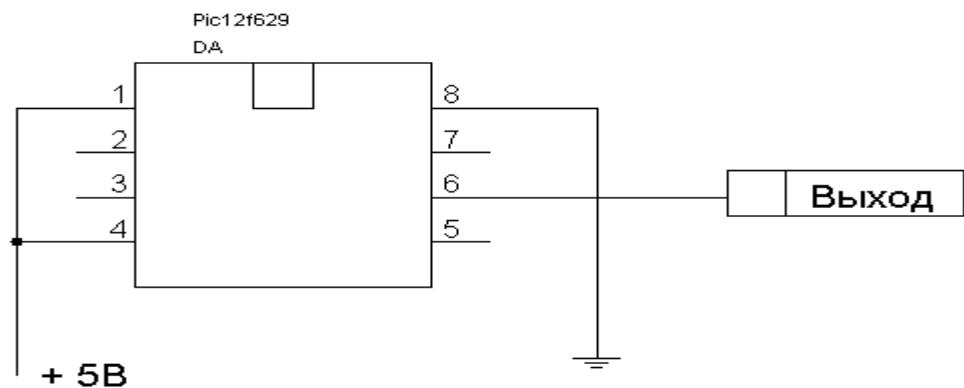

### Генератор шума на микроконтроллере

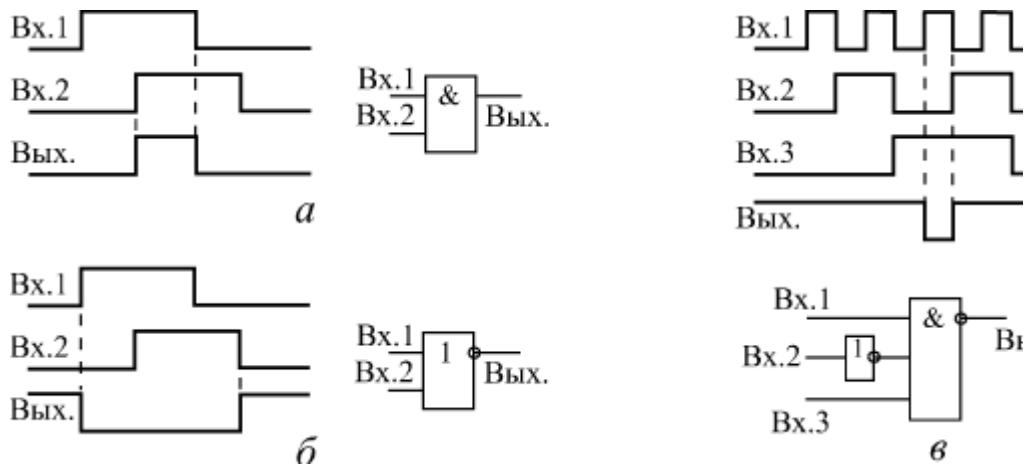

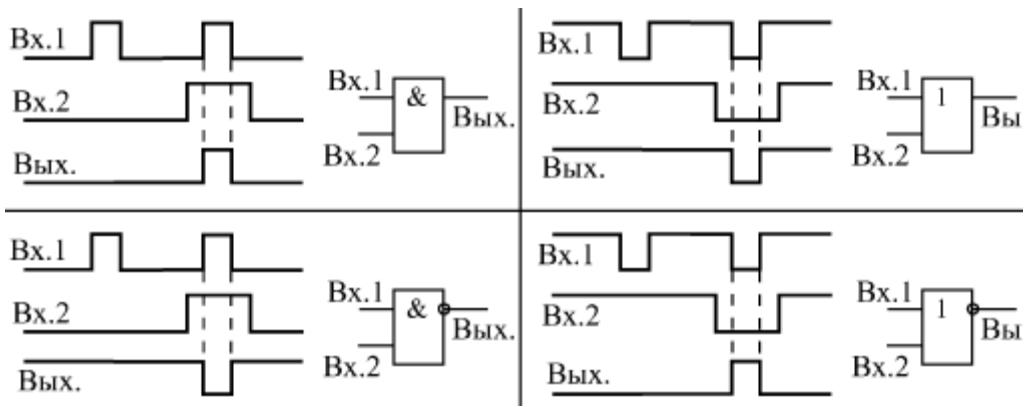

На рисунке 1 приведены примеры формирования элементами выходных сигналов на основании требуемых временных диаграмм входных и выходных сигналов. В случае (1а) выходной сигнал должен быть равен единице при двух единичных входных сигналах, следовательно, достаточно элемента 2И. В случае (1б) выходной сигнал должен быть равен нулю, когда хотя бы один из входных сигналов равен единице, следовательно, требуется элемент 2ИЛИ-НЕ. Наконец, в случае (1в) выходной сигнал должен быть равен нулю при одновременном приходе единичного сигнала Вх. 1, нулевого сигнала Вх. 2 и единичного сигнала Вх. 3. Следовательно, требуется элемент 3И-НЕ, причем сигнал Вх. 2 надо предварительно проинвертировать.

Рисунок 1- Примеры применения элементов И и ИЛИ

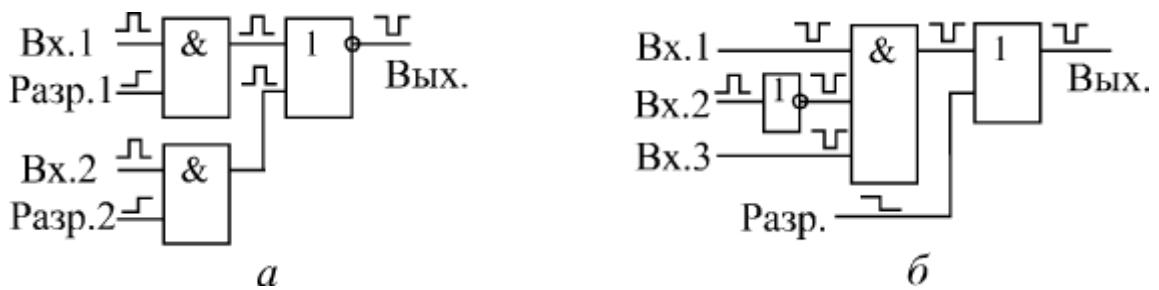

Любой из логических элементов рассматриваемой группы можно рассматривать как управляемый пропускатель входного сигнала (с инверсией или без нее).

Примечание: В случае элемента 2И-НЕ один из входов можно считать информационным, а другой — управляющим. В этом случае при единице на управляющем входе выходной сигнал будет равен проинвертированному входному сигналу, а при нуле на управляющем входе выходной сигнал будет постоянно равен единице, то есть прохождение входного сигнала будет запрещено. Элементы 2И-НЕ с выходом ОК часто используют именно в качестве управляемых буферов для работы на *мультиплексированную* или *двунаправленную линию*.

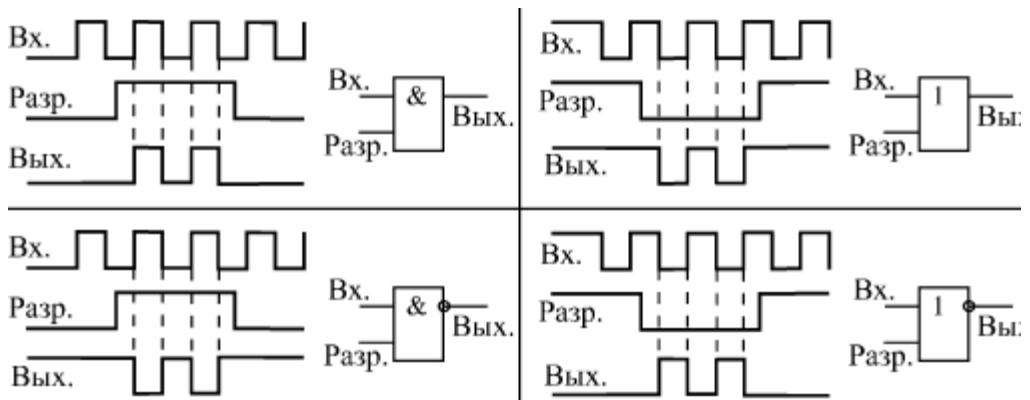

Точно так же в качестве элемента разрешения/запрещения могут применяться элементы И, ИЛИ, ИЛИ-НЕ (рисунок 2). Разница между элементами состоит только в полярности *управляющего сигнала*, в инверсии (или ее отсутствии) входного сигнала, а также в уровне выходного сигнала (нуль или единица) при запрещении прохождения входного сигнала.

Рисунок 2- Разрешение/запрещение прохождения сигналов на элементах И, И-НЕ, ИЛИ, ИЛИ-НЕ

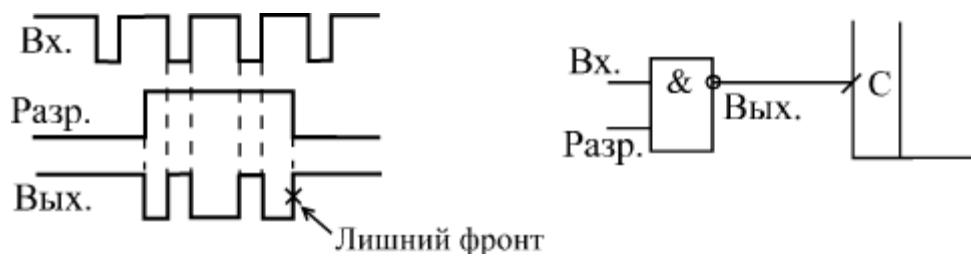

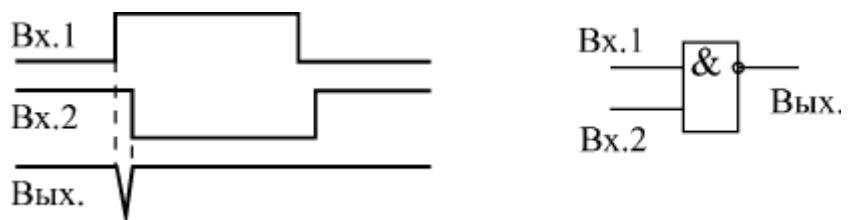

При использовании элементов разрешения/запрещения могут возникнуть дополнительные проблемы в случае, когда сигнал с выхода элемента идет на вход, реагирующий на *фронт сигнала*. В момент перехода из состояния разрешения в состояние запрещения и из состояния запрещения в состояние разрешения в выходном сигнале может появиться дополнительный фронт, никак не связанный с входным сигналом (рисунок 3). Чтобы этого не произошло, надо придерживаться следующего простого правила: если вход реагирует на положительный фронт, то в состоянии запрещения на выходе элемента должен быть нуль, и наоборот.

Рисунок 3 - Появление лишнего фронта при запрещении входного сигнала

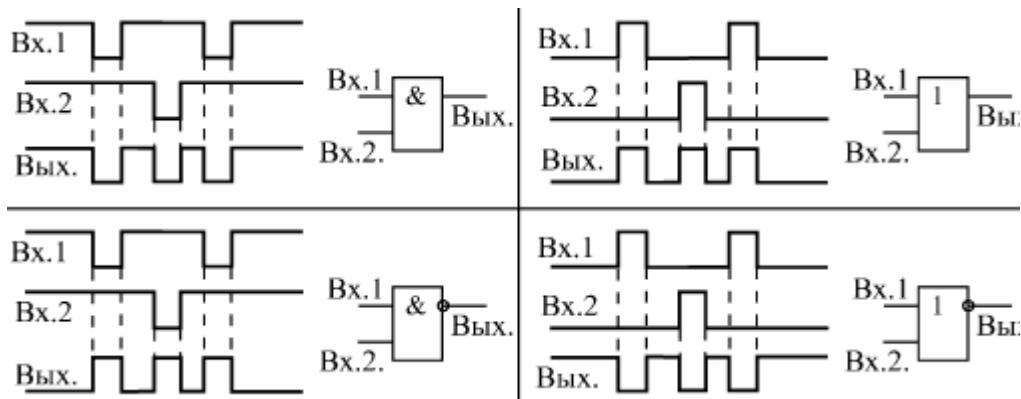

Иногда необходимо реализовать функцию смешивания двух сигналов той или иной полярности. То есть выходной сигнал должен вырабатываться как при приходе одного входного сигнала, так и при приходе другого вход-

ного сигнала. Если оба входных сигнала положительные и выходной сигнал положительный, то получают в чистом виде функцию ИЛИ, и требуется элемент 2ИЛИ. Однако при отрицательных входных сигналах и отрицательном выходном сигнале для такого же смешивания понадобится уже элемент 2И. А если полярность входных сигналов не совпадает с нужной полярностью выходного сигнала, то нужны уже элементы с инверсией (И-НЕ при положительных выходных сигналах и ИЛИ-НЕ при отрицательных выходных сигналах). На рисунок 4 показаны варианты смешивания на разных элементах.

Рисунок 4 - Реализация смешивания двух сигналов

Помимо обозначенных выше видов применения, рассматриваемые элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ иногда бывает удобно применять в качестве схем совпадения различных сигналов. То есть выходной сигнал долженрабатываться тогда, когда сигналы на входах совпадают (приходят одновременно). Если же совпадения нет, то выходной сигнал должен отсутствовать. На [рисунке 5](#) показаны варианты таких схем совпадения на четырех разных элементах. Различаются они полярностями входных сигналов, а также наличием или отсутствием инверсии выходного сигнала.

Рисунок 5 - Схемы совпадения двух сигналов

Примеры совместного использования элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ показаны на [рисунке 6](#).

Рисунок 6 - Примеры совместного использования элементов

Пусть необходимо смешать два сигнала, каждый из которых может быть разрешен или запрещен. Пусть полярность входных сигналов и сигналов разрешения — положительная, а выходной сигнал должен быть отрицательным. В этом случае надо взять два двухходовых элемента И и смешать их выходные сигналы с помощью двухходового элемента ИЛИ-НЕ (6а).

Пусть необходимо смешать два *отрицательных сигнала* и один *положительный сигнал*, причем результирующий сигнал может быть разрешен или запрещен. Полярность сигнала разрешения — отрицательная, полярность выходного сигнала — положительная. Для этого нужно взять трехходовой элемент И, инвертор для положительного входного сигнала и двухходовой элемент ИЛИ (6б).

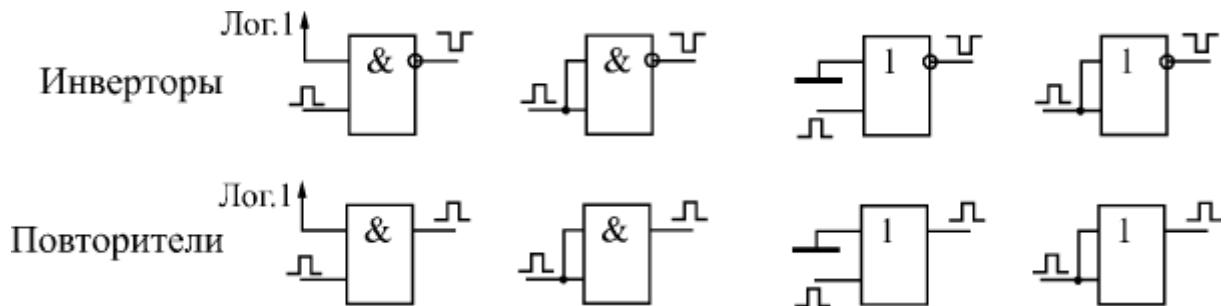

Элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ могут использоваться также в качестве *инверторов* или *повторителей* (рисунок 7), для чего необходимо объединить входы или на неиспользуемые входы подать сигнал нужного уровня. Второе предпочтительнее, так как объединение входов не только увеличивает входной ток, но и несколько снижает быстродействие элементов.

Рисунок 7 - Инверторы и повторители

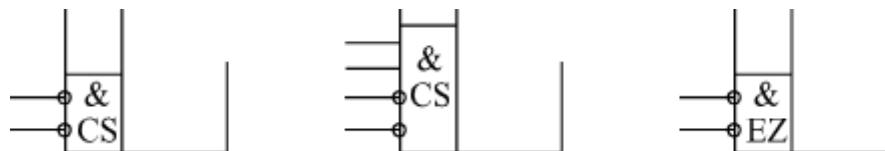

Рисунок 8 - Объединение по И входов микросхем

По функции И часто объединяются входы более сложных микросхем. Иначе говоря, какая-то функция выполняется только тогда, когда на все объединенные по И входы поступают сигналы нужной полярности. Чаще всего по И объединяются входы выбора микросхемы CS и входы управления третьим состоянием выхода микросхемы EZ. На [рисунок 9](#) показано три примера такого объединения по И. При этом надо учитывать, что на инверсные входы для выполнения функции должны поступать нулевые сигналы, а на прямые входы — единичные сигналы. Примерами могут служить микросхемы KP556PT4, KP556PT5, KP1533АП14, KP1533АП15.

До сих пор, рассматривая элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ, мы не выходили за рамки первого уровня представления (*логической модели*). Это вполне допустимо в том случае, когда входные сигналы элементов не меняются одновременно или почти одновременно, когда их фронты разнесены во

времени существенно (больше, чем на время задержки элемента). При одновременном изменении входных сигналов все будет гораздо сложнее необходимо привлекать второй и порой третий уровень представления. В момент изменения входных сигналов выходной сигнал становится неопределенным, нестабильным, непредсказуемым. В результате при неправильном проектировании может не работать вся сложная схема, целый прибор или даже большая система.

Например, возьмем логический элемент 2И-НЕ. Пусть на его входы приходят сигналы, изменяющиеся одновременно, причем в противофазе, то есть один переключается из нуля в единицу, а другой — из единицы в нуль. Пусть по тем или иным причинам (вследствие передачи по проводам, вследствие разных задержек элементов) один из сигналов чуть-чуть сдвинулся во времени относительно другого (рисунок 9). При этом на двух входах в течение кратковременного периода будет присутствовать два единичных сигнала. В результате выход начнет переключаться из единицы в нуль. Он может успеть переключиться, и тогда сформируется короткий импульс. Он может не успеть переключиться, и тогда импульса не будет. Он может иногда успевать переключиться, а иногда не успевать, и тогда выходной импульс то будет появляться, то не будет. Здесь все зависит от быстродействия элемента и величины задержки. Последняя ситуация наиболее неприятна, так как может вызвать нестабильную неисправность, выявить которую крайне сложно.

Рисунок 9 Короткий импульс на выходе элемента 2И-НЕ

На этапе проектирования схемы бороться с такими паразитными импульсами довольно просто: надо всего лишь обеспечить, чтобы вся дальнейшая схема на них не реагировала, например, отключалась на некоторое время после изменения входных сигналов элементов. То есть необходимо временное согласование, синхронизация различных элементов схемы.

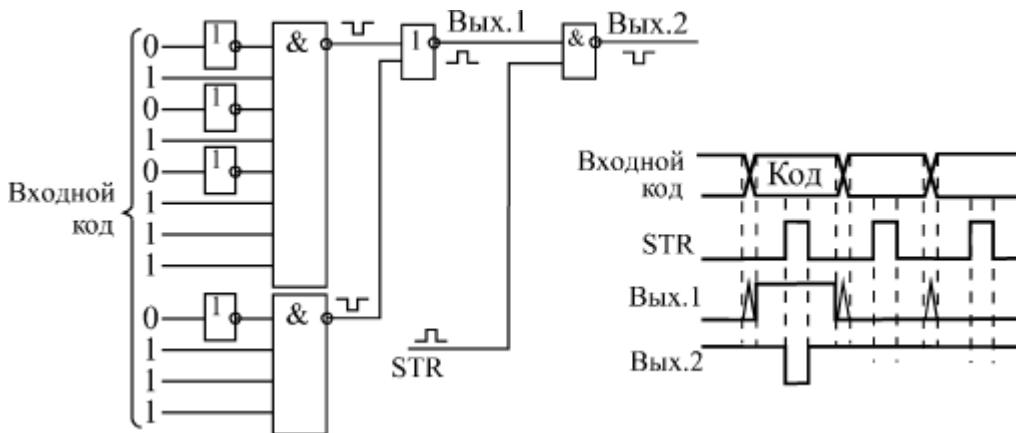

В качестве примера можно рассмотреть один из самых распространенных применений рассматриваемых элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ — селектирование кодов. Суть селектирования сводится к следующему. Пусть имеется некоторая шина, по которой передаются коды. Необходимо выявить появление на этойшине какого-то определенного кода, то есть сформировать выходной сигнал, соответствующий требуемому входному коду.

Схема, выполняющая такую функцию, довольно проста (рисунок 10). В ее основе — многовходовые элементы И-НЕ. При этом сигналы, соответствующие разрядам кода, на которых должны быть единицы, подаются непосредственно на входы элементов И-НЕ. А сигналы, соответствующие разрядам кода, на которых должны быть нули, подаются на входы элементов И-НЕ через инверторы. Выходные сигналы элементов И-НЕ объединяются с помощью элемента ИЛИ-НЕ. В результате на выходе элемента ИЛИ-НЕ формируется сигнал Вых. 1 в тот момент, когда на входе присутствует нужный код.

Однако в момент установления нужного кода и в момент его снятия возникает период неопределенности, когда в выходном сигнале могут быть короткие паразитные импульсы. Это связано как с неодновременным приходом различных разрядов, так и с внутренними задержками нашей схемы. Более того, короткие паразитные импульсы могут возникать на выходе и в том случае, когда любой входной код меняется на любой другой входной код, даже если оба эти кода не селектируются нашей схемой. То есть любое изменение кода всегда сопровождается периодом неопределенности в сигнале Вых. 1.

Рисунок 10 - Селектирование кодов со стробированием

Для этого обычно используется стробирование или тактирование передаваемого кода. То есть, помимо кода, параллельно с ним передается стробирующий или тактирующий сигнал STR, задержанный во времени относительно кода. Активным этот сигнал становится тогда, когда все предыдущие переходные процессы уже завершены, все разряды кода установились в нужные уровни и схема, обрабатывающая код, тоже закончила свою работу. А пассивным он становится, пока еще не начались новые переходные процессы. Это называется вложенным циклом (то есть в нашем случае сигнал STR вложен в сигналы кода). В результате, если мы будем разрешать выходной сигнал нашей схемы Вых. 1 таким сигналом STR с помощью элемента 2И-НЕ, то получим сигнал Вых. 2, свободный от паразитных импульсов и периодов неопределенности.

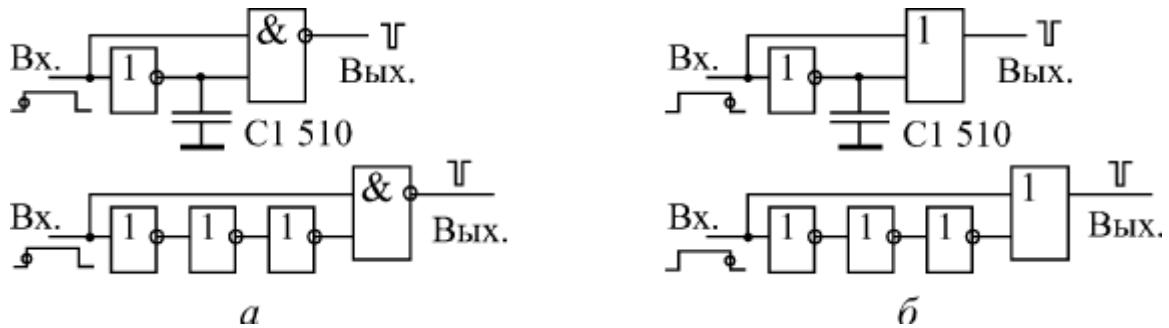

Однако бывают случаи, когда указанная особенность элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ формировать короткие импульсы при изменении входных сигналов оказывается очень полезной. Например, нам необходимо сформировать короткий импульс по положительному или отрицательному фронту имеющегося сигнала. Тогда этот сигнал инвертируют, специально задерживают с помощью цепочки элементов или емкости и подают исходный сигнал и задержанный сигнал на входы элемента (рисунок 11).

Рисунок 11 Формирователи коротких импульсов по фронту входного сигнала

Импульс по положительному фронту входного сигнала формируется на элементе 2И или 2И-НЕ (а), а импульс по отрицательному фронту входного сигнала — на элементе 2ИЛИ или 2ИЛИ-НЕ (б). Если элемент с инверсией, то выходной импульс будет отрицательным, если без инверсии, то положительным. При указанной на схемах величине емкости длительность импульса получается около 50 нс. Для увеличения длительности импульса надо увеличивать величину емкости или же количество *инверторов* в цепи задержки (при этом количество *инверторов* обязательно должно быть нечетным).

Задание: Выбрать способы организации подачи управляющих сигналов для схемы в Задании №2 . Подключить выбранные модули к управляющим входам элементов (регистров, буферных элементов)

## Задание 6 Проектирование цифровых устройств в системе Quartus II

Цель данного раздела заключается в закреплении теоретических знаний, полученных в течение первой недели практического обучения. Результатом выполнения заданий с 4 по 10 является формирования четкого представления о проектировании реально действующих цифровых устройств, роли ПЛИС в современной системе высоких технологий, как средству для моделирования, отладки и проектирования действующих образцов (прототипов), мелкосерийного производства микропроцессорных устройств.

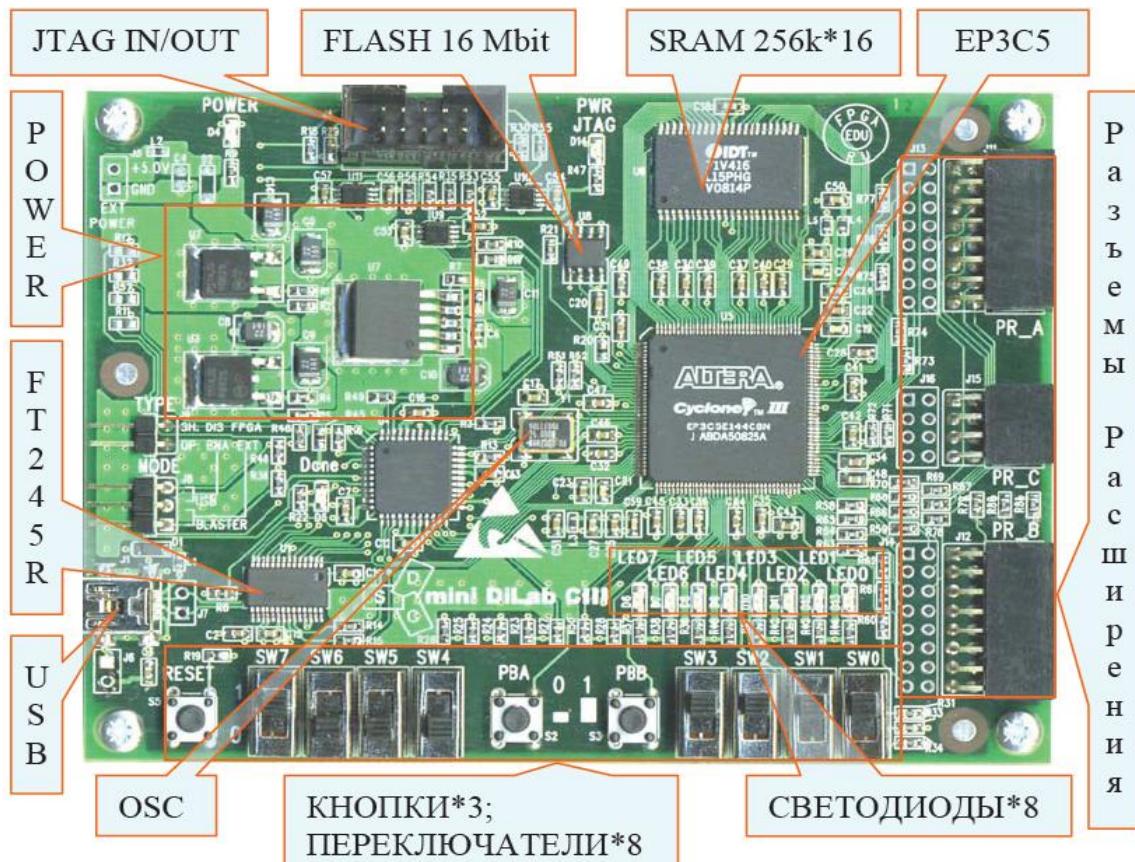

В настоящем задании практикант знакомится с устройством, характеристиками отладочной платы mini- DiLaB (Cyclone 3). Задания, следующие за данным, могут быть реализованы также и на DiLaB (Cyclone 2), при условии соблюдения схемотехнических отличий плат (см. графу Примечние в заданиях).

Внешний вид отладочной платы приведен на рисунке 1.

Рисунок 1 – Внешний вид mini- DiLaB (Cyclone 3)

Как видно из рисунка 1 по функциональному набору периферийных компонентов, данный стенд уступает DiLab II, за кажущейся простотой скрывается достаточно мощное устройство, не обременяющее разработчика излишней связкой периферийных устройств. Данный стенд позволяет сосредоточится на решении конкретных задач. Необходимый набор устройств и компонентов подключается посредством портов расширения.

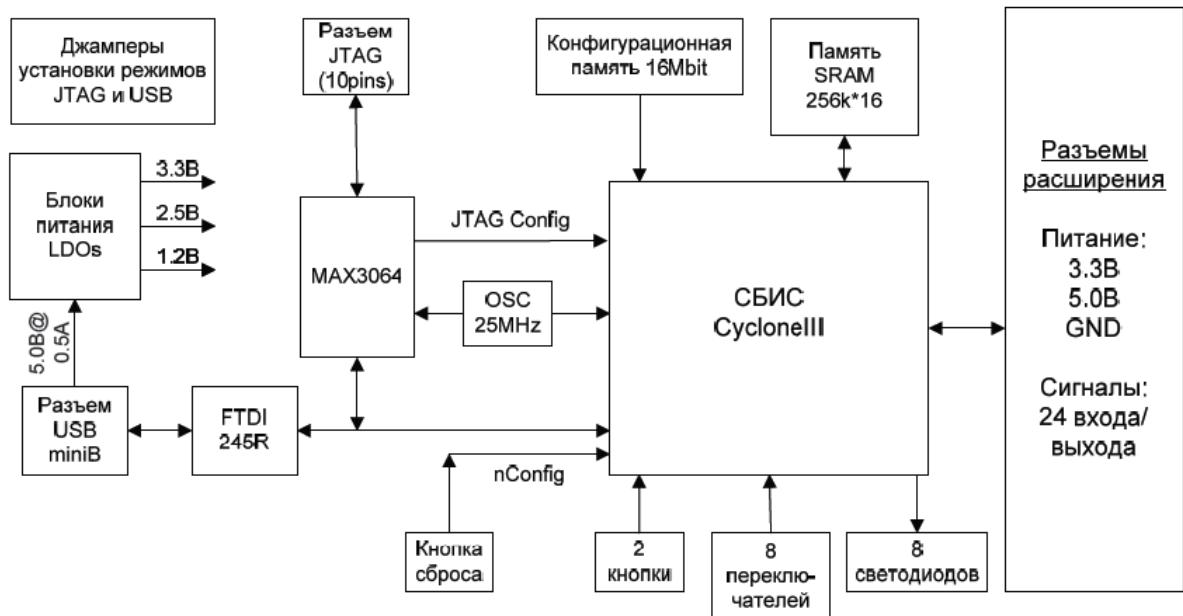

Структурная схема устройства представлена на рисунке 2 ее необходимо зарисовать себе в тетрадь.

Рисунок 2 – Структурная схема стенда

В состав комплекса входят:

- СБИС Программируемой Логики (Cyclone III)

- Конфигурационная память СБИС Cyclone III

- Переключатели

- Кнопки ввода данных

- Светодиоды (8 доступных программисту)

- Микросхема статической памяти (объемом 256k\*16 бит)

- Кварцевый генератор

USB интерфейс, включающий:

- Разъем miniB

- Микросхему FTDI - FT245R

JTAG интерфейс, включающий:

- Микросхему MAX3064

- Набор джамперов для выбора режима работы

- Разъем JTAG

Разъемы расширения

Модуль питания платы.

Центральным элементом стенда является микросхема EP3C5E144C8N (наименование микросхемы надо записать и запомнить). Данная ПЛИС имеет следующие характеристики:

- Число выводов СБИС – 144;

- Число пользовательских выводов (входов/выходов) – 94;

- Число логических элементов – 5136;

- Объем встроенной памяти – 414 кбит;

- Число встроенных умножителей (разрядностью 9\*9) – 46;

- Число встроенных умножителей тактовых сигналов (PLL) – 2;

- Объем файла конфигурации (без сжатия) – 3 Мбит;

Примечание: на плате присутствует кнопка RESET, позволяющая сбросить текущую конфигурацию СБИС.

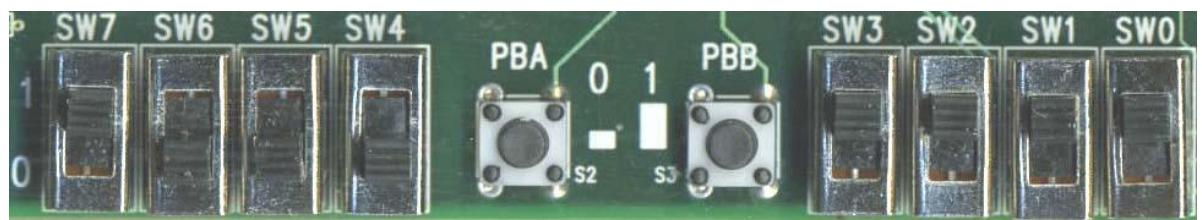

Как было отмечено выше набор компонентов ввода и индикации представлен переключателями (8 шт.), кнопки 2 (шт.), светодиодами (8 шт.), разъемы расширения (в текущей работе не рассматриваются).

### Переключатели:

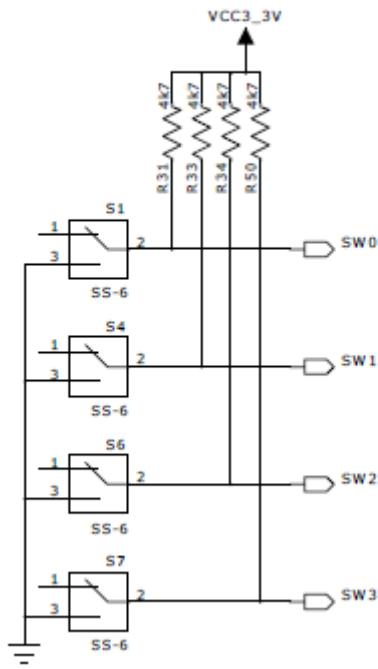

Плата miniDiLaB-СП содержит 8 переключателей. В положении «1» переключатель коммутирует логическую единицу, а в положении «0» - логический нуль (рисунок 3). Верхнее положение – лог. «1», в нижнем – «0»

Рисунок 3

Схема электрическая принципиальная подключения для первых 4 переключателей приведена на рисунке 4, необходимо по аналогии занести в тетрадь схему электрическую принципиальную для кнопок с 5 по 8 занести в тетрадь.

Рисунок 4

В таблице 1 указаны соотношения переключателей с выводами СБИС Cyclone III.

Таблица 1

| Переключатель | Номер вывода<br>EP3C5E144 |

|---------------|---------------------------|

| sw0           | 24                        |

| sw1           | 25                        |

| sw2           | 46                        |

| sw3           | 49                        |

| sw4           | 91                        |

| sw5           | 90                        |

| sw6           | 89                        |

| sw7           | 88                        |

Данную таблицу необходимо занести в тетрадь.

### Кнопки:

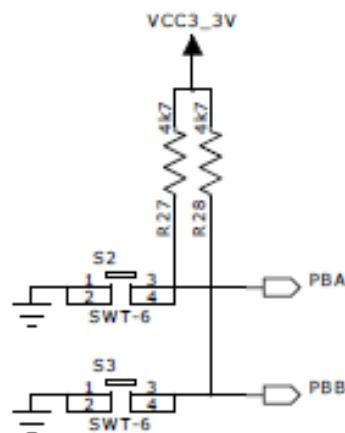

Плата miniDiLaB-СIII содержит 2 кнопки (рисунок 5): при нажатой кнопке передается логический «0», при отжатой – логическая «1»

Рисунок 5

На рисунке 6 представлена схема электрическая принципиальная, в таблице 2 приведены соотношения выводов кнопок с выводами СБИС. Схему и таблицу необходимо занести в тетрадь.

Рисунок 6

| Кнопка | Номер вывода<br>EP3C5E144 |

|--------|---------------------------|

| pba    | 34                        |

| pbb    | 51                        |

Светодиоды:

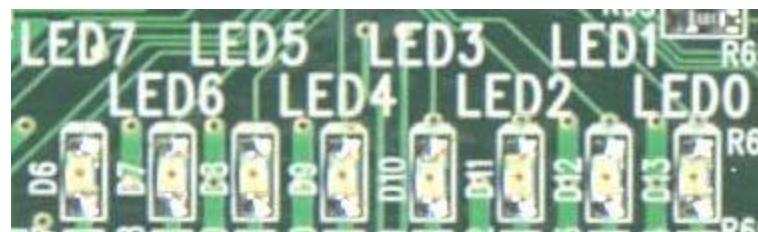

Плата miniDiLaB-CIII содержит 8 светодиодов (рисунок 7).

Рисунок 7–8 Светодиодов для индикации

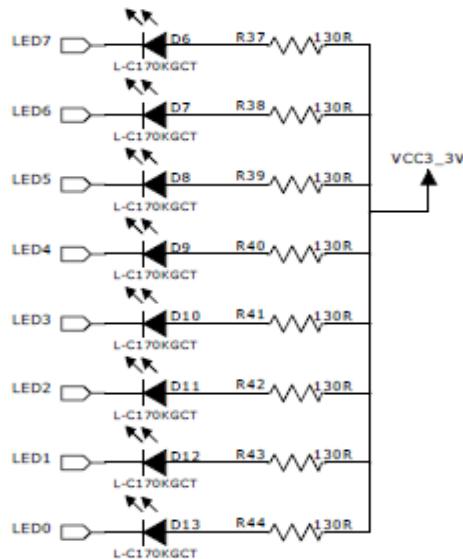

На рисунке 9 представлена схема электрическая принципиальная модуля индикации, в таблице 3 указаны соотношения выводов СБИС и светодиодов, которые необходимо занести в тетрадь

Рисунок 8

Таблица 3

| Светодиод | Номер выво-да<br>EP3C5E144 | Активный<br>(включаю-<br>щий светоди-<br>од) уровень<br>сигнала |

|-----------|----------------------------|-----------------------------------------------------------------|

| led0      | 64                         | лог. «0»                                                        |

| led1      | 50                         | лог. «0»                                                        |

| led2      | 59                         | лог. «0»                                                        |

| led3      | 58                         | лог. «0»                                                        |

| led4      | 55                         | лог. «0»                                                        |

| led5      | 54                         | лог. «0»                                                        |

| led6      | 53                         | лог. «0»                                                        |

| led7      | 52                         | лог. «0»                                                        |

## **Кварцевый генератор**

На плате miniDiLaB-СП используется тактовый генератор GXO-7531 (25 MHz). Таблица 4 содержит сведения соединения выводов микросхемы генератора с выводами СБИС CycloneIII (занести в тетрадь).

Таблица 4

| Имя сигнала | Номер вывода<br>EP3C5E14<br>4 |

|-------------|-------------------------------|

| clk_25mhz   | 22                            |

### **Самостоятельно:**

1. Изучить подключение к статическому ОЗУ

2. Занести в тетрадь сведения о JTAG интерфейсе, используемый для конфигурирования (состояние перемычек).

### **Вопросы:**

1. Какой тип подключения используют светодиоды (общий катод, общий анод), как влияет тип данного подключения на управляющие выходы СБИС?

2. Какова емкость статической оперативной памяти в байтах?

3. Какие значения должны быть на перемычке для выбора конфигурирования СБИС от встроенного USB-Blaster?

4. Какие уровни напряжения применяются на плате?

## **Задание 7 Проектирование цифровых устройств в системе Quartus II.**

### **«Бегущий огонь»**

Цель: самостоятельно пройти процесс проектирования от постановки задачи, до реализации работающего устройства.

Задача: спроектировать цифровое устройство выполняющее, поочередное включение/выключение светодиодов.

Описание:

Разрабатываемое устройство позволяет сформировать простейшее тестовое устройство, реализующее пошаговое включение светодиодов «Бегущий огонь» время переключения между диодами составляет порядка 1с.

Алгоритм работы (записать в отчет):

- деление на счетчике частоты 25Mhz на  $2^{**}23$ ;

- поочередное включение (активный уровень – логический нуль)/выключение светодиодов при помощи счетчика – дешифратора (0-7).

В САПР Quartus II создать новый проект (**Примечание:** при работе с Cyclone II выбрать соответствующую СБИС).

В появившемся окне введите следующие данные как показано в таблице 1.

Таблица 1

| Параметр мастера                                                                                                                      | Наименование  |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------|

| <b>What is the working directory for this project?</b><br><br>Рабочая папка ( <i>с помощью браузера найти рабочую папку проекта</i> ) | ...\\begushiy |

| <b>What is the name of this project?</b><br><br>Имя проекта                                                                           | begushiy      |

| <b>What is the name of the top-level design entity for this project?</b><br><br>Имя модуля верхнего уровня в иерархии проекта.        | begushiy      |

В окне Family & Device Setting выбрать:

- в разделе **Family** задать Cyclone III;

- тип корпуса в графе **Package** задать – TQFP;

- в графе **Pin count** задать - 144,

- в разделе **Available devices** выбрать СБИС **EP3C5E144C8**

По окончанию создания проекта создать новый файл Block Diagram/Schematic File. Сохранить файл под тем же именем что и проект.

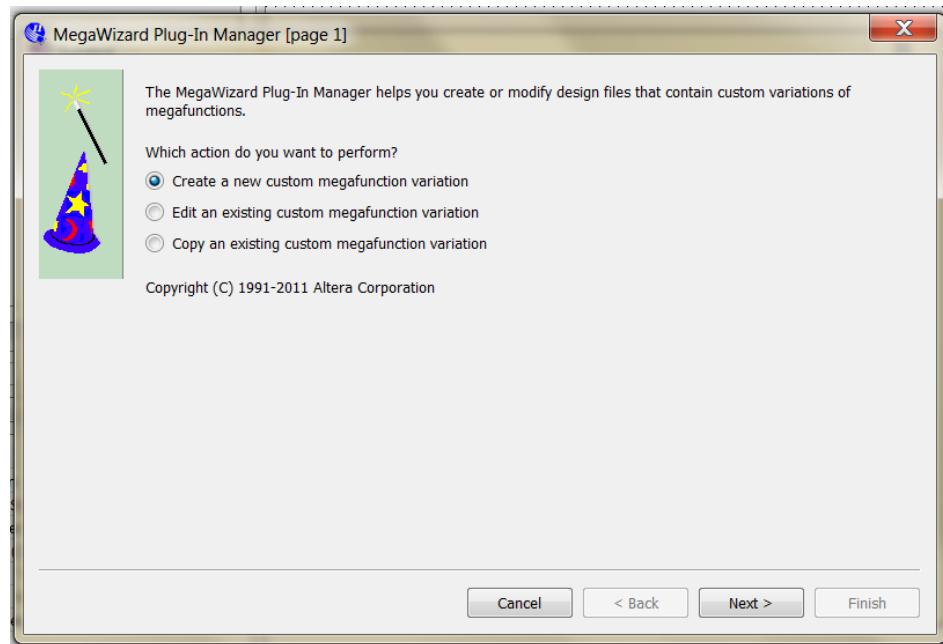

1. Вызвать мастер Mega Wizard Plug-in Manager, через меню Tools – Mega Wizard Plug-in Manager.

1.1 В окне 1 выбрать «Create a new custom megafunction variatrion»

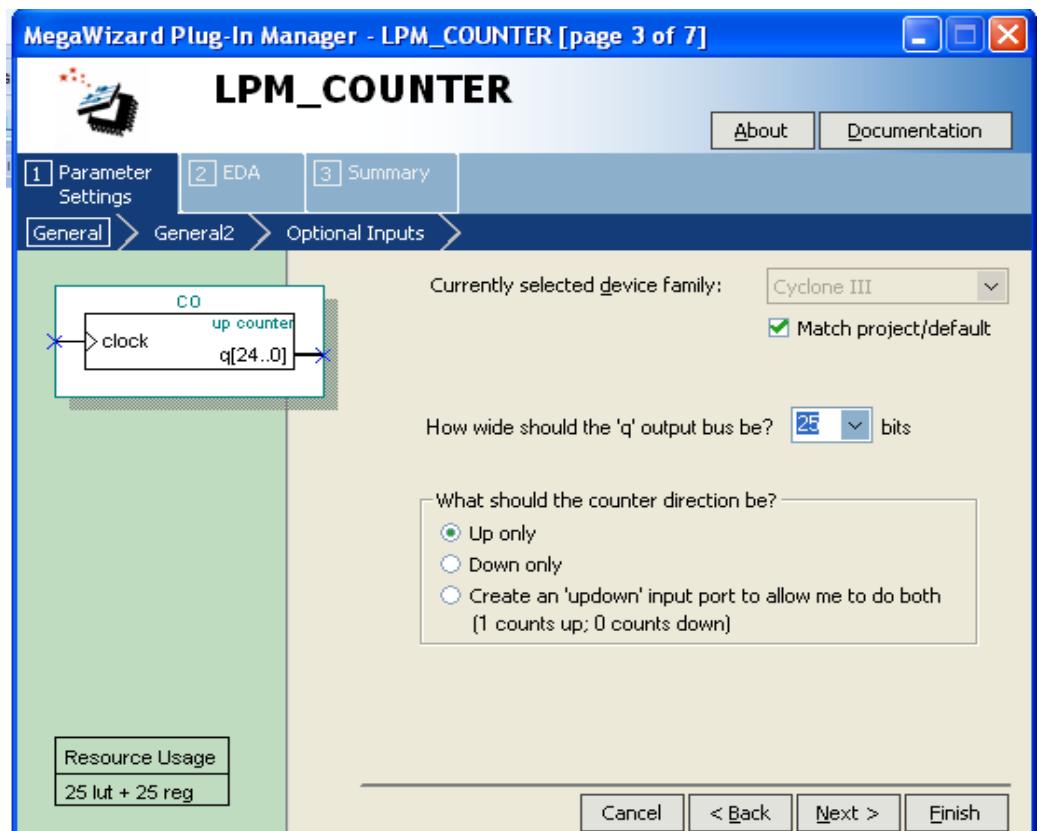

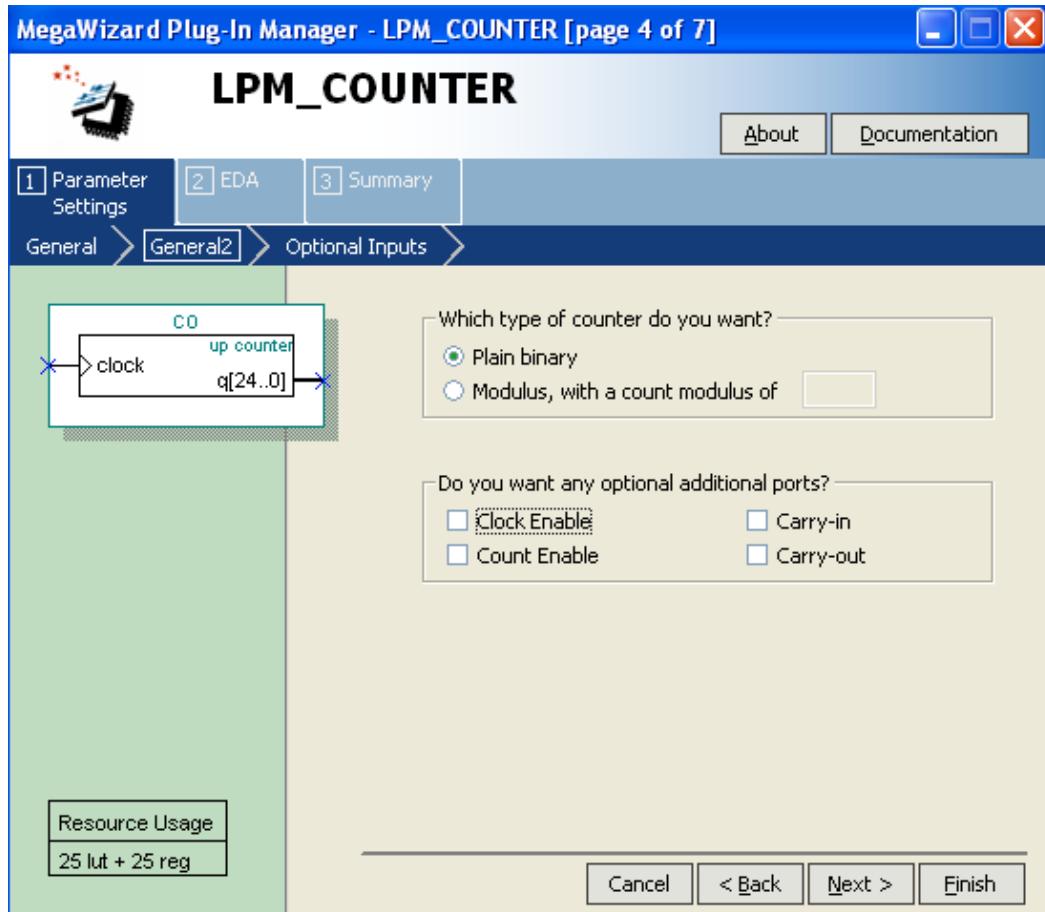

1.2 В окне 2 перейти в раздел Arithmetic, выбрать пункт LPM\_COUNTER, задать имя выходного файла, count, в качестве языка описания выбрать VHDL, нажать кнопку Next

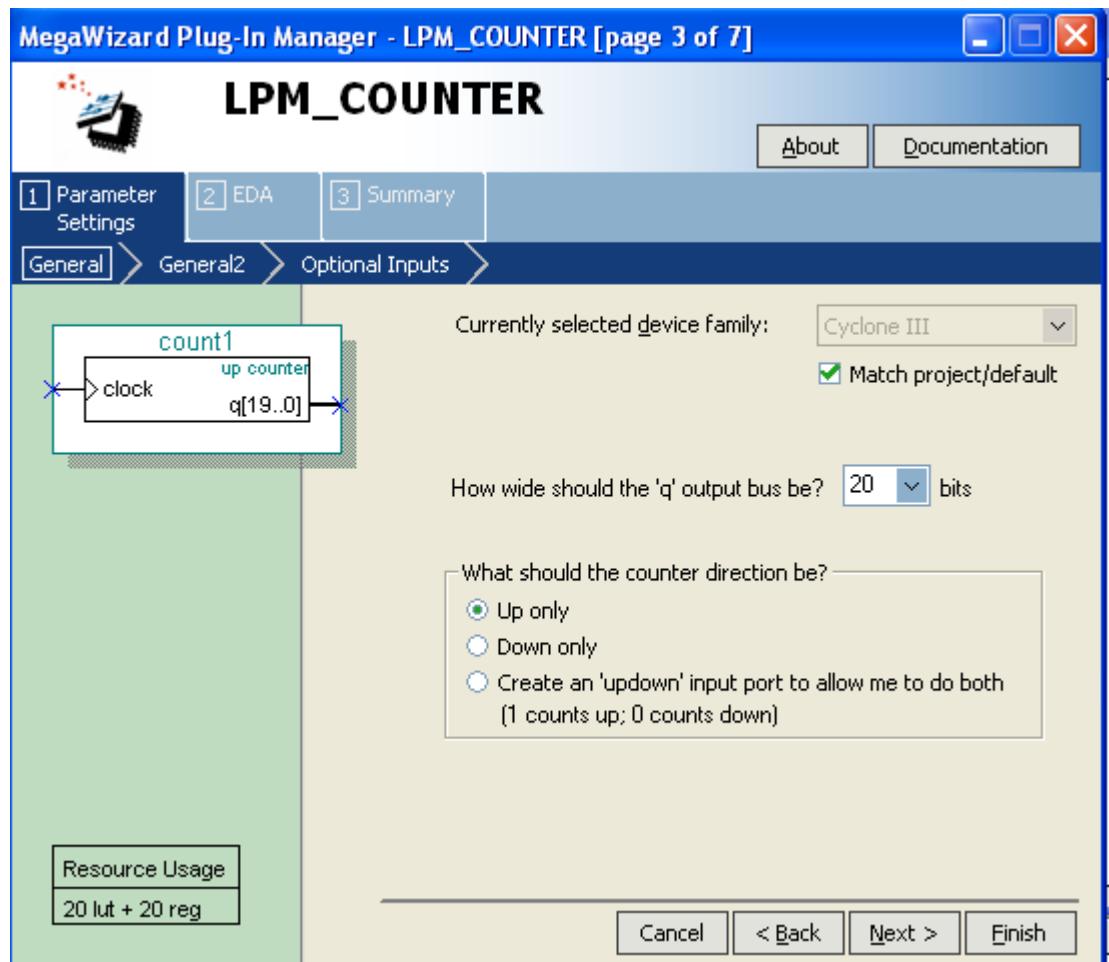

1.3 Проектируется суммирующий счетчик с максимальным количеством перебора 33 554 432. На рисунке 1 представлено окно с параметрами, которые необходимо задать:

- ширина шины q = 25 бит;

- счетчик суммирующий «up only»

По окончании нажать Next

Рисунок 1

2.4 На рисунке 2 представлено окно параметров счета, входов управления счетом, флагов переноса – необходимо выбрать только параметр «Plain binary» в разделе «Which type of counter do you want»

Рисунок 2

2.5 В появившемся окне «Optional Inputs» осуществляется назначение синхронных/ асинхронных входов загрузки, сброса, установки в максимальное значение. Все эти опции оставить пустыми. Нажать Next дважды.

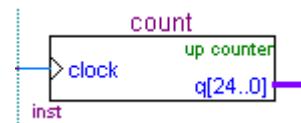

2.6 Нажать Finish. В рабочей библиотеке появился компонент count (рисунок 3). Параметры созданного счетчика должны быть отражены в отчете.

Рисунок 3

2. Далее необходимо создать второй счетчик со встроенным дешифраторм от 0 до 7, к которому будут подключены светодиоды [led 0-7].

Данный элемент следует описать на языке VHDL, для этого необходимо в меню File-New выбрать VHDL File. На рисунке 4 представлен листинг, описывающий компонент.

3.

```

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use IEEE.numeric_std.ALL;

entity led is port

(clk: in std_logic;

led: out std_logic_vector(7 downto 0));

end led;

architecture led_arch of led is

signal cnt: integer range 0 to 7 :=0;

begin

process (clk)

begin

if rising_edge(clk) then

if cnt=7 then

cnt<=0;

else

cnt<=cnt+1;

end if;

end if;

end process;

led(0)<= '1' when cnt=0 else '0';

led(1)<= '1' when cnt=1 else '0';

led(2)<= '1' when cnt=2 else '0';

led(3)<= '1' when cnt=3 else '0';

led(4)<= '1' when cnt=4 else '0';

led(5)<= '1' when cnt=5 else '0';

led(6)<= '1' when cnt=6 else '0';

led(7)<= '1' when cnt=7 else '0';

end led arch;

```

Рисунок 4

Данный листинг занести в отчет и составить комментарии к нему.

Сохранить файл под именем led.vhd, выполнить команду меню File- Create/Update – Create Symbol Files for Current File. В библиотеке появится новый компонент с именем led.

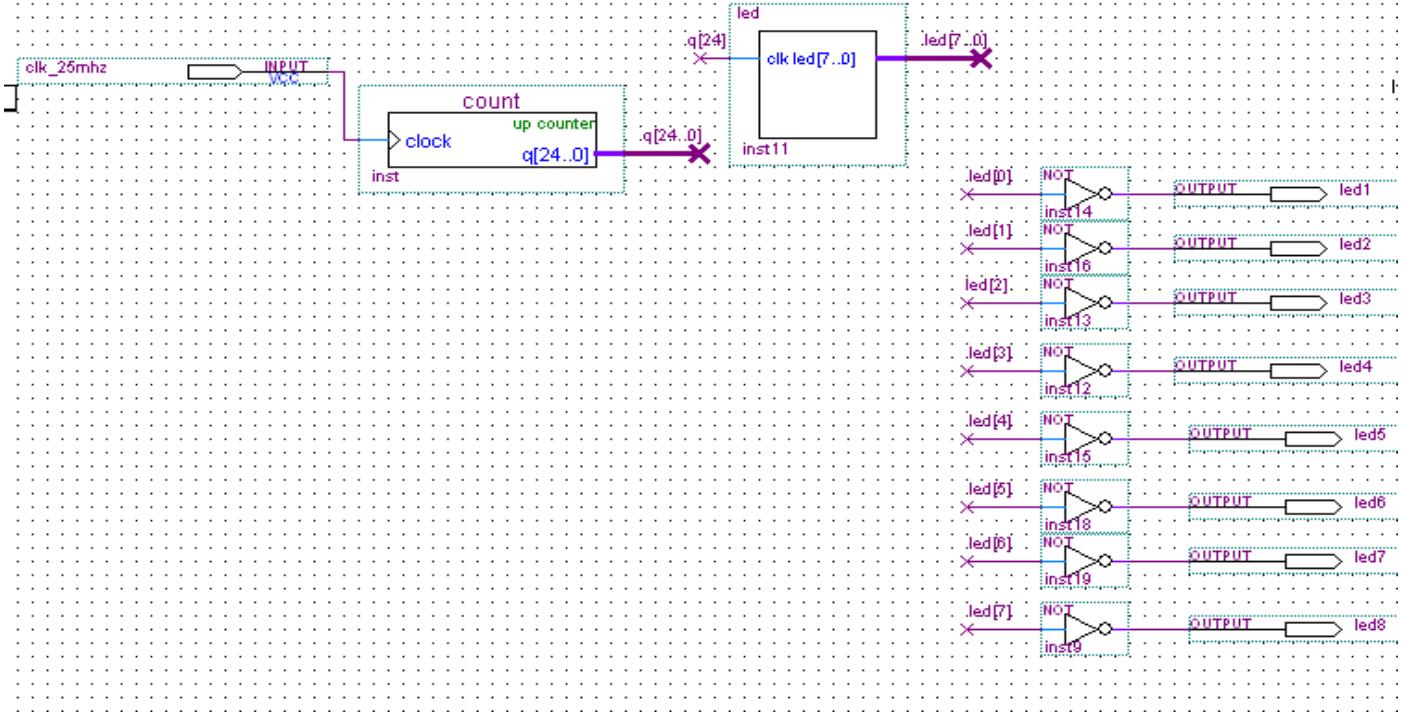

4. Осуществить начертание схемы как показано на рисунке 5.

Примечание: имена проводников и шин задаются в разделе Properties – Name, при выделении проводника.

Рисунок 5

Имена шин, проводников и выводов должны быть сохранены, так как показано на рисунке.

**Примечание:** Данная схема разработана и отлажена на примере mini – DiLaB (Cyclone 3). При выполнении и отладке на плате DiLaB- II (Cyclone II ) необходимо учитывать, что светодиоды на ней подключены по схеме с общим катодом, поэтому устанавливать инверторы на выходе нельзя! При не соблюдении данного условия появится эффект поочередного отключения светодиодов.

5. Осуществить проверку синтаксиса схемы. Для этого в меню Processing выполнить команду Start=>Start Analysis & Elaboration.

6. Перейти в инструмент Assignments - Pin Planner и выполнить назначение выводов на СБИС (ПЛИС) выводам схемы, как показано на рисунке 6 (выводы СБИС для решения задачи можно получить из отчета к заданию №4).

**Примечание:** При выполнении и отладке на плате DiLaB- II (Cyclone II ) необходимо применять сведения по выводам из документации к плате, использование имен выводов как для платы mini – DiLaB (Cyclone 3) недопустимо !

|    | Node Name   | Direction | Location | I/O Bank |   |

|----|-------------|-----------|----------|----------|---|

| 1  | clk_25mhz   | Input     | PIN_22   | 1        | E |

| 2  | led1        | Output    | PIN_64   | 4        | E |

| 3  | led2        | Output    | PIN_60   | 4        | E |

| 4  | led3        | Output    | PIN_59   | 4        | E |

| 5  | led4        | Output    | PIN_58   | 4        | E |

| 6  | led5        | Output    | PIN_55   | 4        | E |

| 7  | led6        | Output    | PIN_54   | 4        | E |

| 8  | led7        | Output    | PIN_53   | 3        | E |

| 9  | led8        | Output    | PIN_52   | 3        | E |

| 10 | <new node>> |           |          |          |   |

Рисунок 6

7. С помощью команды **Processing => Start Compilation** осуществить полную компиляцию проекта.

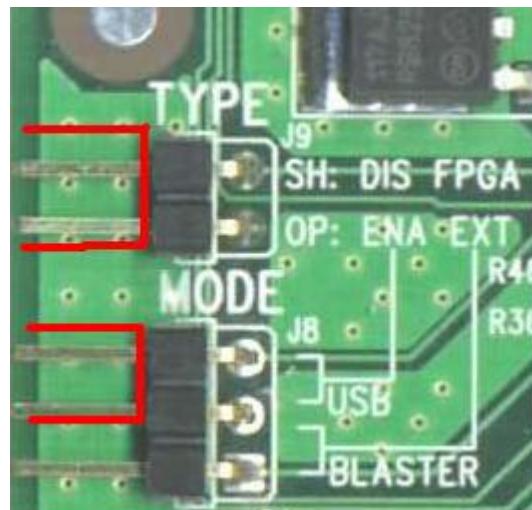

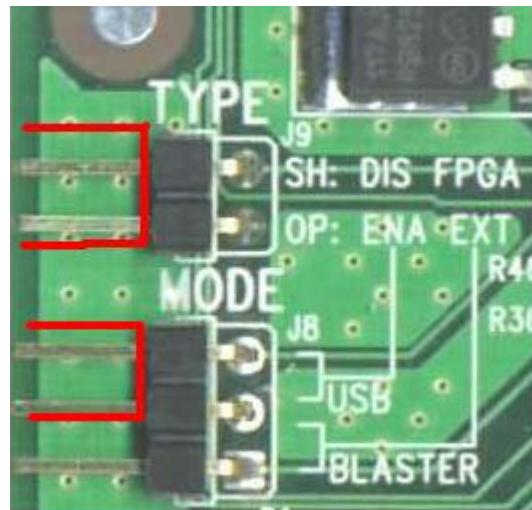

8. Конфигурирование платы:

- На плате miniDiLaB-CIII установить джамперы следующим образом (рисунок 7):

- a. Соединить выводы разъема “TYPE”

- b. Соединить выводы 1-2 разъема “MODE”

- Подсоединить, входящий в комплект поставки USB кабель A-miniB к USB 2.0 порту компьютера (должен обеспечивать ток до 500mA), а затем к плате miniDiLaB-III.

Рисунок 7

**Примечание:** При конфигурировании платы DiLaB- II (Cyclone II ) необходимо подключить блок питания, подключить внешний USB- Blaster, включить тумблер I/O.

Выполнить команду **Tools=> Programmer** или кликнуть по значку главного меню (рисунок 8)

Рисунок 8

Откроется окно управления конфигурированием СБИС.

Для установки интегрированного на плату miniDiLaB-СIII средства конфигурирования СБИС нажать кнопку **Hardware Setup**, откроется окно настроек в нем выбрать **USB- Blaster**.

Светодиод led[7..0], для которого разрешена работа (счетчик содержит значение данного светодиода ) будет светится и гаснуть, следующим загорится светодиод номер которого будет следующим.

Работа выполнена успешно

При выполнении работы ее результаты необходимо предоставить преподавателю, необходимо представить аккуратно оформленный отчет.

### **Самостоятельно (обязательны для выполнения):**

1. Добавить кнопку pba в качестве сигнала Reset для счетчика – делителя

2. Используя переключатели SW [1..2] изменить работу схемы таким образом, что при включенном в положение лог «1» SW 1 схема работала с текущей скоростью, при переключении SW 2 в положение лог «1» скорость переключения светодиодов увеличилась ~ в 2 раза. При положении обоих переключателей в лог. «0» схема не работает, горит текущий светодиод. **Внимание в один момент времени в лог «1» находится один переключатель.**

Вопросы:

1. Назначение выводов Carry –out, Set, Load у счетчиков

2. Как изменить код описания счетчика-десифратора, чтобы «бегущий огонь» начинался с led 7 и шел до led 0 (ответ в виде частоты кода в отчете)

### **Задание 8 Проектирование цифровых устройств в системе Quartus II**

#### **«Генератор псевдослучайных последовательностей»**

Цель: самостоятельно пройти процесс проектирования от постановки задачи, до реализации работающего устройства.

Задача: спроектировать цифровое устройство выполняющее, формирование псевдослучайных последовательностей (генератор случайных чисел).

Описание:

Разрабатываемое устройство позволяет переходить в один момент времени в состояние (формировать уникальный двоичный код).

Алгоритм работы (записать в отчет):

- установлено некое начальное число (обратная связь);

- при нажатии кнопки «PB\_A» с тактового генератора поступает серия синхроимпульсов на вход сдвиговых регистров.

- случайным образом выбранные выходы с регистров объединены логическими элементами «mod2», выход с элементов заведен на последовательный вход сдвигового регистра.

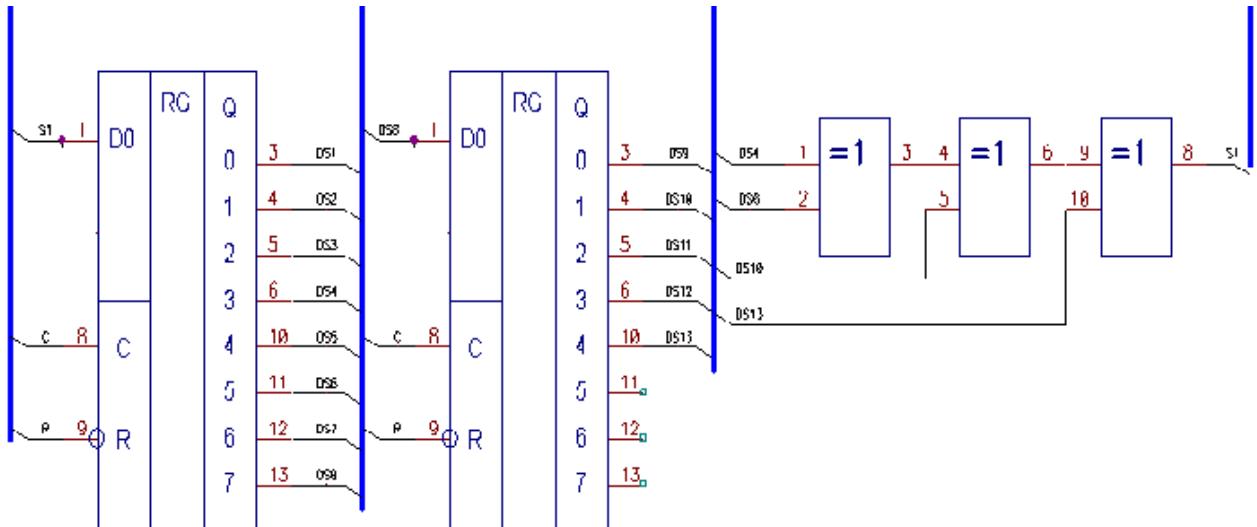

Схема, реализующая формирование псевдослучайных последовательностей представлена на рисунке 1.

Рисунок 1

Цепи обратной связи (DS4, DS6, DS10, DS13) заведены на элементы =1. При прекращении тактовой последовательности схема сохраняет свое состояние. По положительному фронту тактового сигнала (С) сдвиговые регистры осуществляют сдвиг с занесением нового значения. Следующее поступление тактовых сигналов вызывает смену состояний регистров по некоторому закону, зависящему от цепи обратной связи (DS4, DS6, DS10, DS13) элементов =1. При этом генерируется псевдослучайная последовательность. Статические характеристики последовательности нулей и единиц, получаемых с выхода любого триггера, близки к характеристикам случайной последовательности и тем ближе к ней, чем больше разрядность регистра сдвига.

В САПР Quartus II создать новый проект (**Примечание:** при работе с Cyclone II выбрать соответствующую СБИС).

В появившемся окне введите следующие данные как показано в таблице 1.

Таблица 1

| Параметр мастера                                                                                                               | Наименование |

|--------------------------------------------------------------------------------------------------------------------------------|--------------|

| <b>What is the working directory for this project?</b><br><br>Рабочая папка ( с помощью браузера найти рабочую папку проекта)  | ... \ crypto |

| <b>What is the name of this project?</b><br><br>Имя проекта                                                                    | crypto       |

| <b>What is the name of the top-level design entity for this project?</b><br><br>Имя модуля верхнего уровня в иерархии проекта. | crypto       |

В окне Family & Device Setting выбрать:

- в разделе **Family** задать Cyclone III;

- тип корпуса в графе Package задать – TQFP;

- в графе Pin count задать - 144,

- в разделе **Available devices** выбрать СБИС **EP3C5E144C8**

9. По окончанию создания проекта создать новый файл Block Diagram/Schematic File. Сохранить файл под тем же именем что и проект.

10. Вызвать мастер Mega Wizard Plug-in Manager, через меню Tools – Mega Wizard Plug-in Manager.

- 10.1 В окне 1 выбрать «Create a new custom megafunction variatrion»

- 10.2 В окне 2 перейти в раздел Arithmetic, выбрать пункт LPM\_COUNTER, задать имя выходного файла, count, в качестве языка описания выбрать VHDL, нажать кнопку Next

- 10.3 Задать ширину шины q =20 бит. На рисунке 2 представлено окно с параметрами, которые необходимо задать:

- ширина шины q = 20 бит;

- счетчик суммирующий «up only»

По окончании нажать Next

Рисунок 2

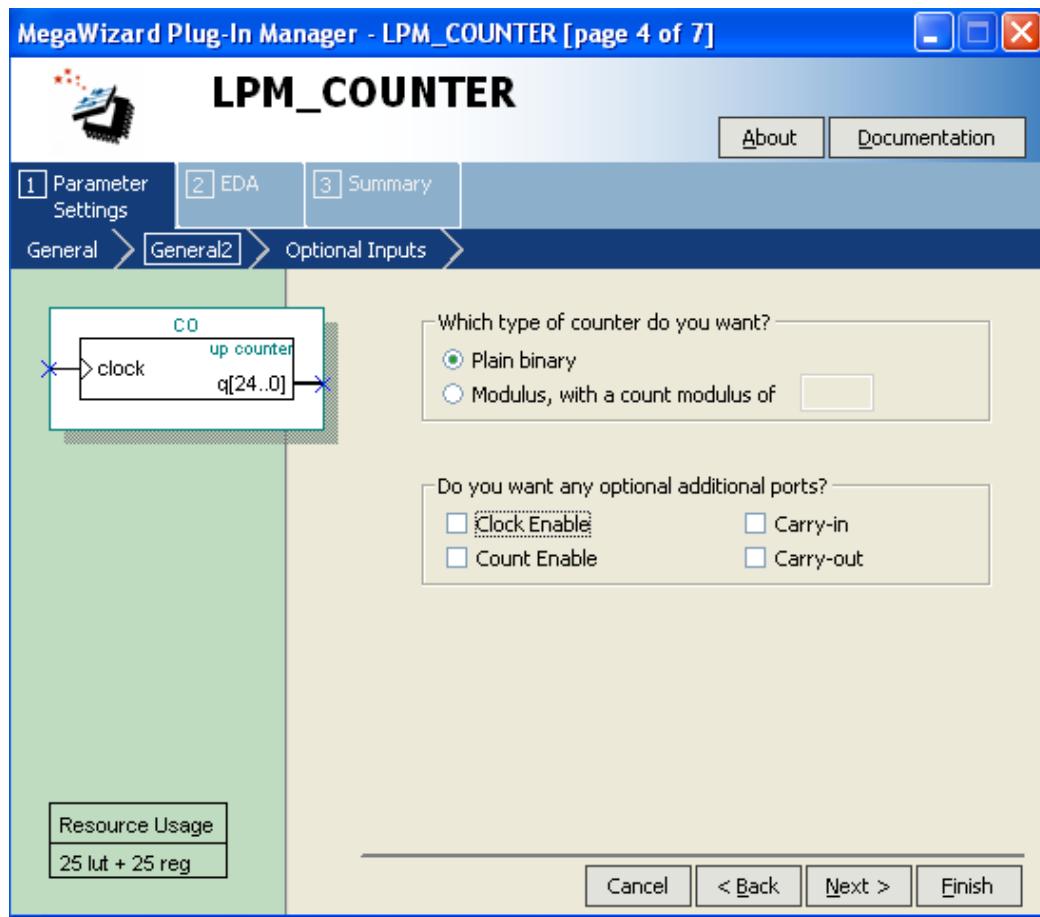

2.4 На рисунке 3 представлено окно параметров счета, входов управления счетом, флагов переноса – необходимо выбрать только параметр «Plain binary» в разделе «Which type of counter do you want»

Рисунок 3

2.7 В появившемся окне «Optional Inputs» осуществляется назначение синхронных/ асинхронных входов загрузки, сброса, установки в максимальное значение. Все эти опции оставить пустыми. Нажать Next дважды.

2.8 Нажать Finish. В рабочей библиотеке появился компонент count (рисунок 4). Параметры созданного счетчика должны быть отражены в отчете.

Рисунок 4

11. Далее необходимо создать 8 –разрядный последовательно – параллельный сдвиговый регистр, входом синхронизации и разрешением работы, сброс (добавить самостоятельно). Библиотечный элемент расположен в

Storage Installed Plug-In    В таблице 2 приведены значения параметров регистра, которые необходимо выставить. Данный элемент следует создать по аналогии с предыдущим.

Таблица 2

| Параметр мастера                                                                           | Наименование                                                                                                    |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| <b>Which direction do you want the register to shift?</b><br>Определить направление сдвига | Right (сдвиг вправо)                                                                                            |

| <b>How wide should the ‘q’ output bus be</b><br>Ширина шины данных выхода , бит            | 8                                                                                                               |

| <b>Which outputs do you want?</b><br>Какой тип шины выхода данных.                         | Data output (параллельный выход)                                                                                |

| <b>Do you want any optional inputs?</b><br>Какие дополнительные входы выбрать?             | Clock Enable input (вход управления - синхронизация)<br>Serial shift data input<br>Последовательный вход данных |

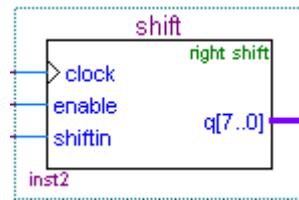

На рисунке 5 представлен компонент сдвигового регистра.

Рисунок 5

В библиотеке появится новый компонент с именем shift.

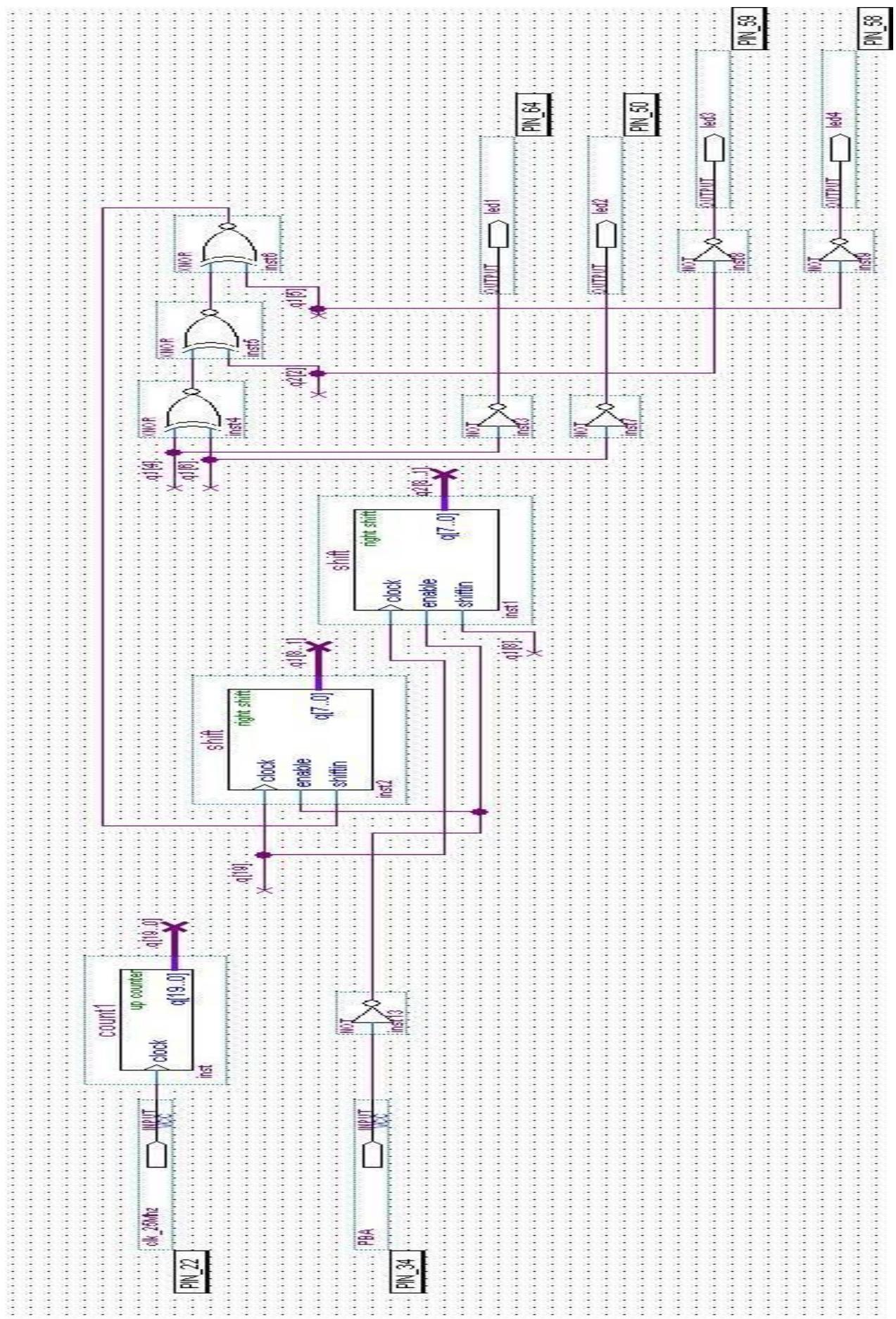

12. Осуществить начертание схемы как показано на рисунке 6.

Примечание: имена проводников и шин задаются в разделе

Properties – Name, при выделении проводника.

**Примечание:** Данная схема разработана и отлажена на примере mini – DiLaB (Cyclone 3). При выполнении и отладке на плате DiLaB- II (Cyclone II ) необходимо учитывать, что светодиоды на ней подключены по схеме с общим катодом, поэтому устанавливать инверторы на выходе нельзя!

13. Осуществить проверку синтаксиса схемы. Для этого в меню Processing выполнить команду Start=>Start Analysis & Elaboration.

14. Перейти в инструмент Assignments - Pin Planner и выполнить назначение выводов на СБИС (ПЛИС) выводам схемы, как показано на рисунке 6 (выводы СБИС для решения задачи можно получить из отчета к заданию №4).

**Примечание:** При выполнении и отладке на плате DiLaB- II (Cyclone II ) необходимо применять сведения по выводам из документации к плате, использование имен выводов как для платы mini – DiLaB (Cyclone 3) недопустимо!

|   | Node Name    | Direction | Location | I/O Bank |

|---|--------------|-----------|----------|----------|

| 1 | clk_25Mhz    | Input     | PIN_22   | 1        |

| 2 | led1         | Output    | PIN_64   | 4        |

| 3 | led2         | Output    | PIN_50   | 3        |

| 4 | led3         | Output    | PIN_59   | 4        |

| 5 | led4         | Output    | PIN_58   | 4        |

| 6 | PBA          | Input     | PIN_34   | 2        |

| 7 | <<new node>> |           |          |          |

Рисунок 6

15. С помощью команды **Processing => Start Compilation** осуществить полную компиляцию проекта.

16. Конфигурирование платы:

- На плате miniDiLaB-CIII установить джамперы следующим образом (рисунок 7):

- a. Соединить выводы разъема “TYPE”

- b. Соединить выводы 1-2 разъема “MODE”

- Подсоединить, входящий в комплект поставки USB кабель A-miniB к USB 2.0 порту компьютера (должен обеспечивать ток до 500mA), а затем к плате miniDiLaB-CIII.

Рисунок 7

**Примечание:** При конфигурировании платы DiLaB- II (Cyclone II) необходимо подключить блок питания, подключить внешний USB- Blaster, включить тумблер I/O.

Выполнить команду **Tools=> Programmer** или кликнуть по значку главного меню (рисунок 8)

Рисунок 8

Откроется окно управления конфигурированием СБИС.

Для установки интегрированного на плату miniDiLaB-СIII средства конфигурирования СБИС нажать кнопку **Hardware Setup**, откроется окно настроек в нем выбрать **USB- Blaster**.

Светодиоды led[4..1], будут загораться в некотором порядке при нажатии на кнопку РВА. При опускании кнопки РВА светодиоды будут гореть, что соответствует некоторому псевдослучайному числу. При повторном нажатии на кнопку РВА, состояние светодиодов изменится.

Работа выполнена успешно

При выполнении работы ее результаты необходимо предоставить преподавателю, необходимо представить аккуратно оформленный отчет.

**Самостоятельно (обязательны для выполнения):**

1. Добавить кнопку РВВ в качестве асинхронного сигнала Reset для сдвиговых регистров (предварительно добавив данный вход для регистра)

2. Подключите все 8 светодиодов к выходам второго сдвигового регистра. При выполнении работы на плате DiLaB- II (Cyclone II ) необходимо к выходам подключить к дешифратору семисегментного кода и подключить индикатору.

Вопросы:

1. Применение генераторов случайных чисел?

2. Как изменить закономерность формирования случайного кода? Напишите закон формирования псевдослучайной последовательности для данной схемы (пример:  $Y= R1[Q1]\&R2[Q7]$ )

## Задание 9 Создание знакогенератора

1. Описать содержимое постоянной памяти знакогенератора для вывода строки HELLO WORLD, описание символов знакогенератора приведено в таблице1 (повторяющиеся символы не требуют для своего хранения в памяти ячеек – они просто выбираются при помощи повторной ссылки на их адрес)

| Символ | Соответствие на индикаторе abcdefg | Семисегментный индикатор                                                          | Адрес ячейки, содержащей символ |

|--------|------------------------------------|-----------------------------------------------------------------------------------|---------------------------------|

| h      | 0010111                            |  | 000                             |

| E      | 1001111                            |                                                                                   | 001                             |

| L      | 0001110                            |                                                                                   | 010                             |

| O      | 1111110                            |                                                                                   | 011                             |

| W      | 0011100                            |                                                                                   | 100                             |

| R      | 1100111                            |                                                                                   | 101                             |

| D      | 0111101                            |                                                                                   | 110                             |

1. Создайте файл с расширением .mif при помощи команды File – New – Memory Initialization File

2. В диалоге Number of Words... введите в поле Number of Words – 7, в поле Word Size -7.

3. Выберете View – Address Radix – Binary, Memory Radix – Binary.

4. Заполните ячейки памяти как показано на рисунке 1.

| Addr | +00     | +01     | +10     | +11     |

|------|---------|---------|---------|---------|

| 000  | 0010111 | 1001111 | 0001110 | 1111110 |

| 100  | 0011100 | 1100111 | 0111101 |         |

Рисунок 1

5. Создайте новый файл для редактирования схемы электрической принципиальной.

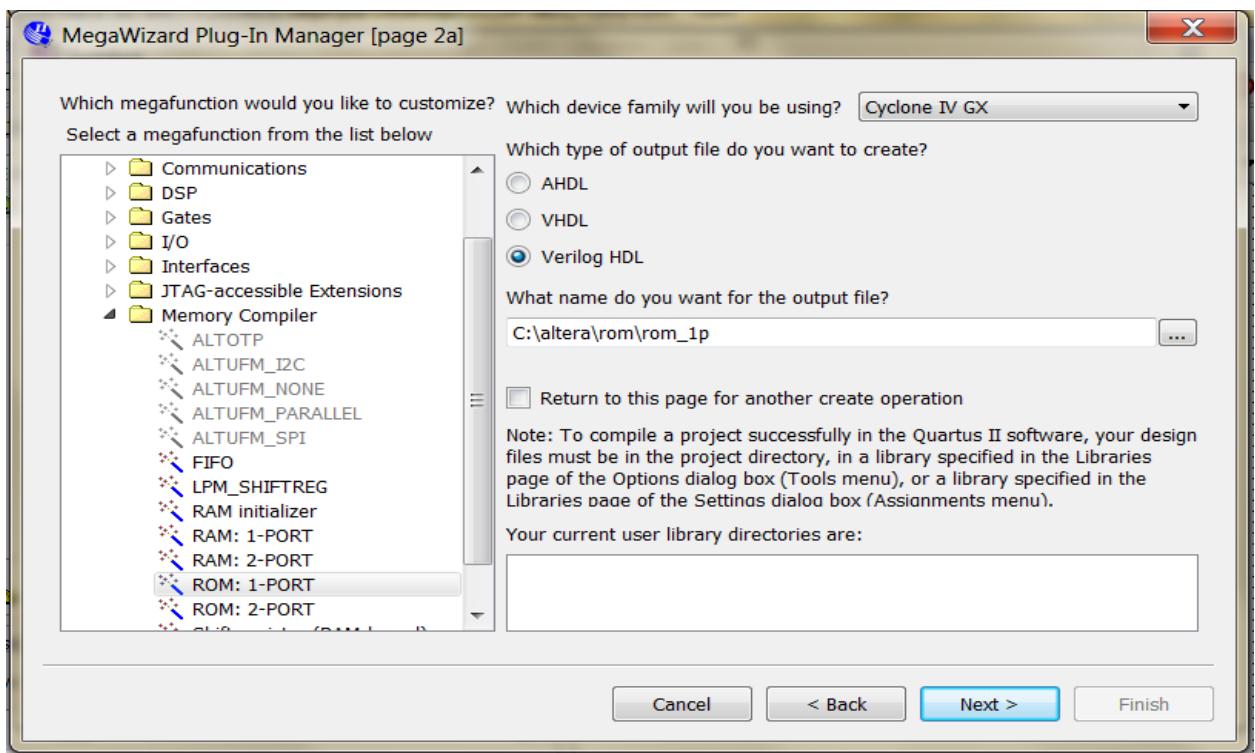

6. Далее вызвать MegaWizard Plug-In Manager (рисунок 2), выбрать пункт «Create....

Рисунок 2

7. На втором шаге мастера в разделе Memory Compiler выбрать – ROM 1 – PORT. Присвоить имя выходному файлу rom\_1p (рисунок 3) нажать «Next».

Рисунок 3

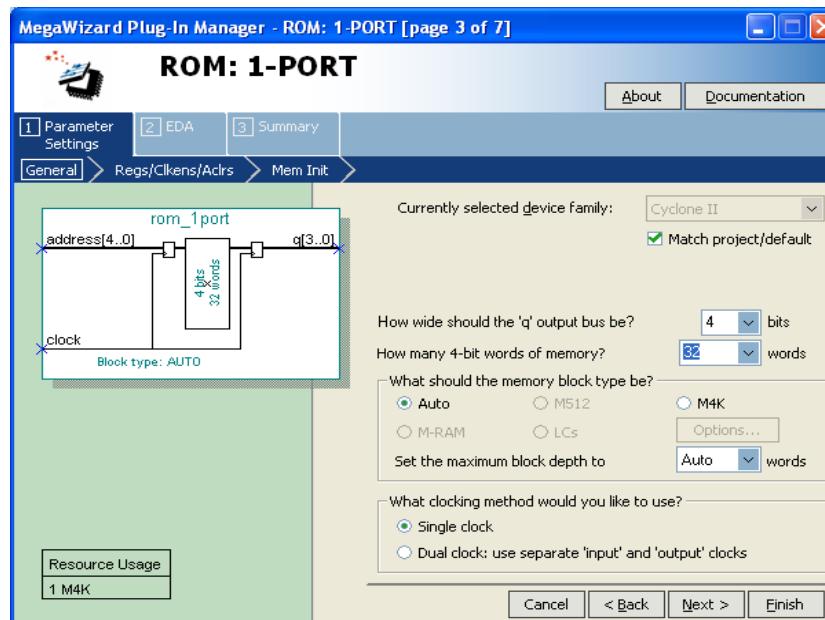

8. Во вновь открывшемся окне для поля «How wide should the 'q' output bus be» - установить 7 бит;

9. Во втором поле «How many 4 –bit words of memory» установить значение 7.

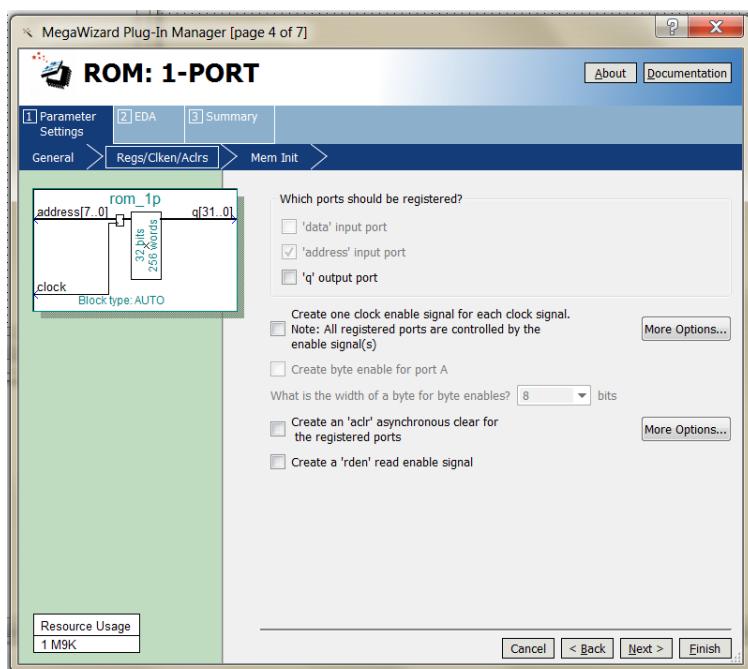

Остальные поля оставить неизменными как на рисунке 4. Нажать кнопку «Next». В открывшемся окне оставить все поля по умолчанию и нажать кнопку «Next»(рисунок 5).

Рисунок 4

Рисунок 5

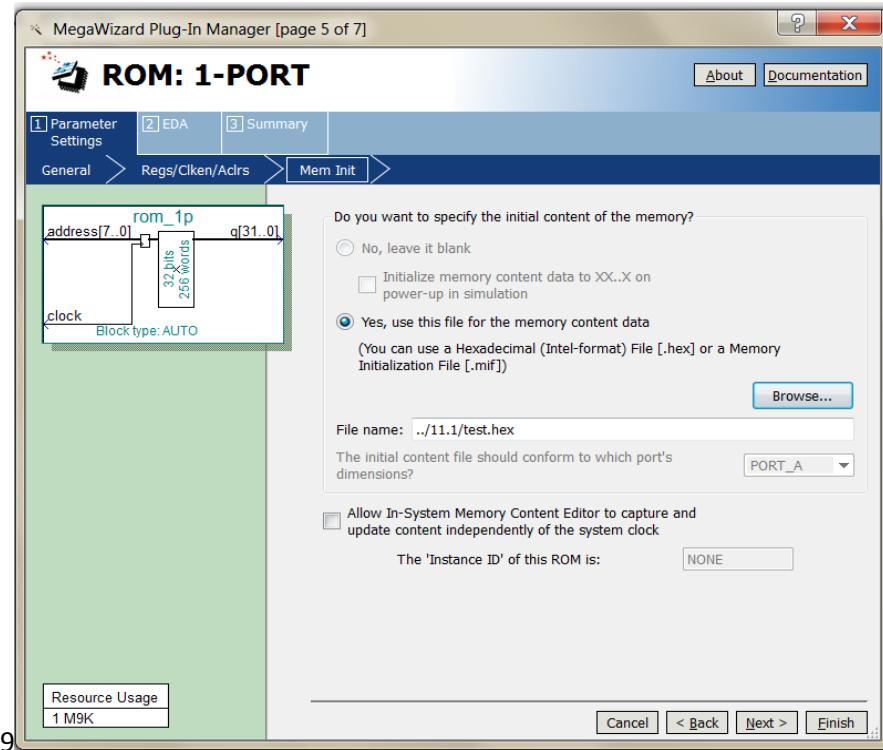

10. В открывшемся окне выбрать ранее созданный файл с прошивкой rom1.hex (рисунок 6)

Рисунок 5

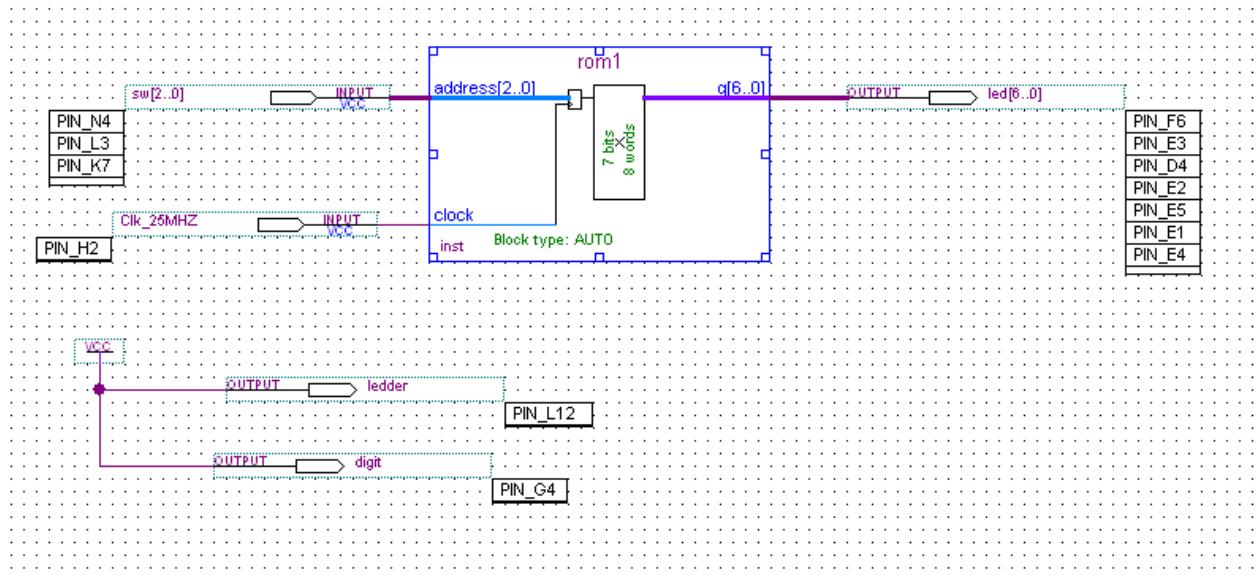

11. Шины адреса ПЗУ будет подключена к переключателям sw1- sw 3, выходная шину данных ПЗУ подключена к семисегментному индикатору. Построить схему как показано на рисунке 7.

Рисунок 7

12. После компиляции переключателями переберите значения памяти и убедитесь в верности отображения символов в памяти. Попробуйте по-

очередно перебирая составить слово «hELLO WOPLD» - так должно отображаться

### Задание 10 Создание бегущей строки

Для вывода сообщения в режиме бегущей строки необходимо выводить символы из знакогенератора в соответствии с заданной последовательностью, а именно перебирать ячейки памяти с адресами, содержащими выводимые символы.

Так для вывода строки «Hello WORLD» необходимо 11 раз перебрать адреса с ячейками символов. В таблице 1 предыдущего раздела описаны адреса и соответствующие им символы. В таблице 2 представлено содержимое памяти rom2, в которой последовательно хранятся адреса ячеек знакогенератора.

Таблица 2

| Символ | Адрес ячейки с символом в rom1 | Содержимое ячейки rom2 | Адрес ячейки rom2 |

|--------|--------------------------------|------------------------|-------------------|

| H      | 000                            | 000                    | 0000              |

| E      | 001                            | 001                    | 0001              |

| L      | 010                            | 010                    | 0010              |

| L      | 010                            | 010                    | 0011              |

| O      | 011                            | 011                    | 0100              |

| W      | 100                            | 100                    | 0101              |

| O      | 011                            | 011                    | 0110              |

| R      | 101                            | 101                    | 0111              |

| L      | 010                            | 010                    | 1000              |

| D      | 110                            | 110                    | 1001              |

По принципу, описанному в предыдущем разделе создайте файл rom2.mif и поместите по адресам в столбце 4, содержимое ячеек столбец 3 (рисунок 8).

| Addr | +00 | +01 | +10 | +11 |

|------|-----|-----|-----|-----|

| 0000 | 000 | 001 | 010 | 010 |

| 0100 | 011 | 100 | 011 | 101 |

| 1000 | 010 | 110 |     |     |

Рисунок 8

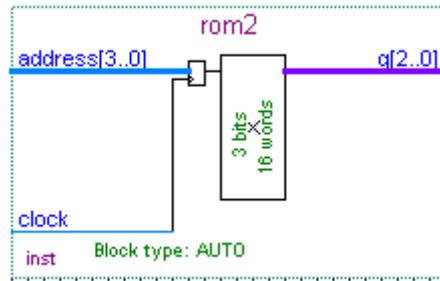

По принципу описанному в предыдущем разделе создайте память ROM, с количеством хранимых слов 10, разрядностью – 3 бита (рисунок 9).

Рисунок 9

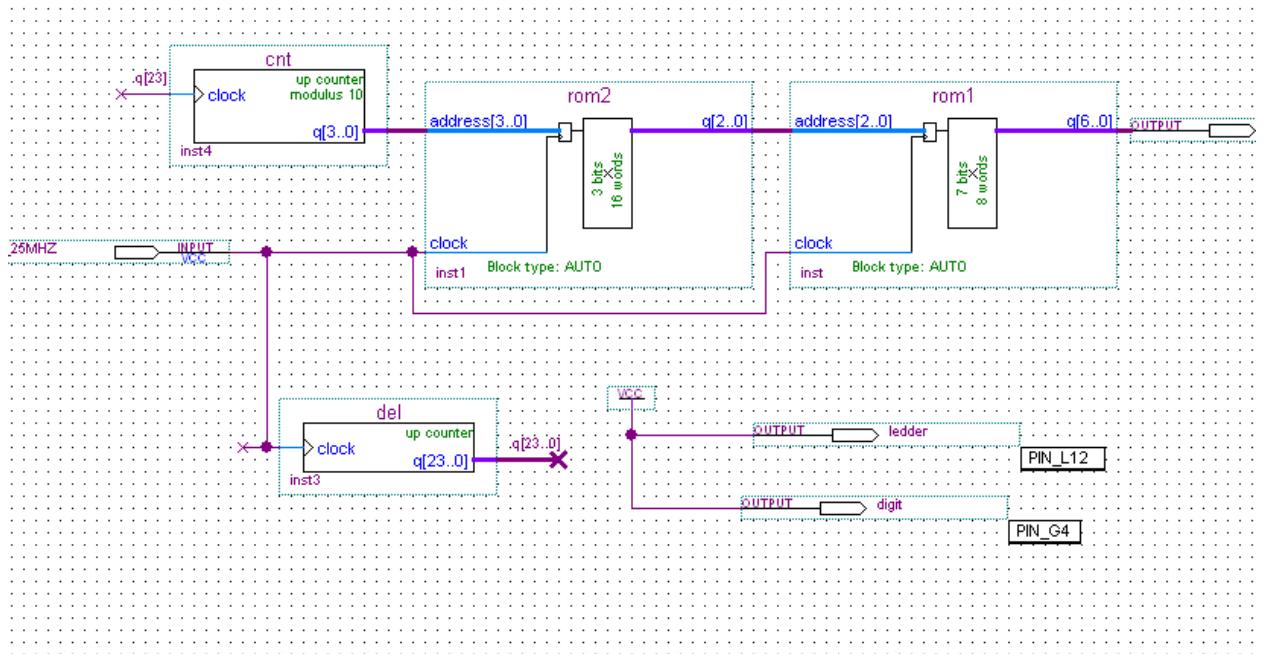

По принципу разобранному в предыдущих работах построить счетчик на сложение с модулем пересчета до 10, а также делитель частоты 25МГц, подключить счетчик к 23 разряду делителя. Выход памяти q[2..0] rom2, подключить к адресной шине address [2..0] памяти rom1.

Общая схема подключения показана на рисунке 10.

Рисунок 10

При правильном выполнении задания на первом индикаторе должна постепенно выводиться заданная фраза.

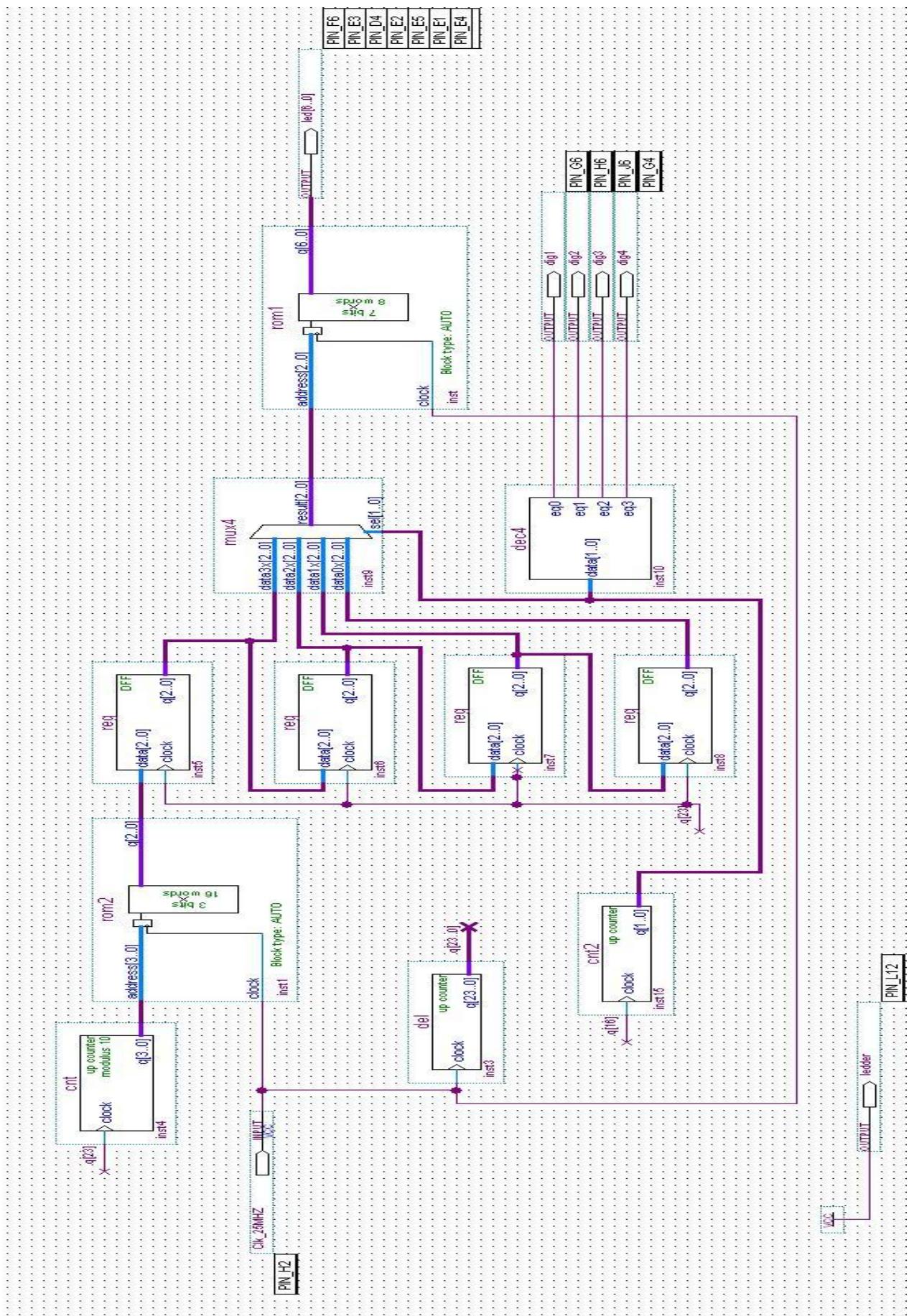

Самостоятельно построить изменить схему (рисунок 10), как показано на рисунке 11.

## Рисунок 11